# Model Sim®

## SE

**Tutorial**

Version 5.7e

Published: 29/Apr/03

The world's most popular HDL simulator

ModelSim /VHDL, ModelSim /VLOG, ModelSim /LNL, and ModelSim /PLUS are produced by Model Technology™, a Mentor Graphics Corporation company. Copying, duplication, or other reproduction is prohibited without the written consent of Model Technology.

The information in this manual is subject to change without notice and does not represent a commitment on the part of Model Technology. The program described in this manual is furnished under a license agreement and may not be used or copied except in accordance with the terms of the agreement. The online documentation provided with this product may be printed by the end-user. The number of copies that may be printed is limited to the number of licenses purchased.

ModelSim is a registered trademark and Signal Spy, TraceX, ChaseX and Model Technology are trademarks of Mentor Graphics Corporation. PostScript is a registered trademark of Adobe Systems Incorporated. UNIX is a registered trademark of AT&T in the USA and other countries. FLEXIm is a trademark of Globetrotter Software, Inc. IBM, AT, and PC are registered trademarks, AIX and RISC System/6000 are trademarks of International Business Machines Corporation. Windows, Microsoft, and MS-DOS are registered trademarks of Microsoft Corporation. OSF/Motif is a trademark of the Open Software Foundation, Inc. in the USA and other countries. SPARC is a registered trademark and SPARCstation is a trademark of SPARC International, Inc. Sun Microsystems is a registered trademark, and Sun, SunOS and OpenWindows are trademarks of Sun Microsystems, Inc. All other trademarks and registered trademarks are the properties of their respective holders.

Copyright © 1990 -2003, Model Technology, a Mentor Graphics Corporation company. All rights reserved. Confidential. Online documentation may be printed by licensed customers of Model Technology and Mentor Graphics for internal business purposes only.

Model Technology 8005 Boeckman Road, Bldg. E4 Wilsonville, OR 97070 USA

phone: (503) 685-0820 fax: (503) 685-0910

e-mail: support@model.com, sales@model.com

home page: http://www.model.com

support page: <a href="http://www.model.com/support">http://www.model.com/support</a>

## **Table of Contents**

| Introduction                                            |

|---------------------------------------------------------|

| Lesson 1 - Creating a Project                           |

| Lesson 2 - Basic VHDL simulation                        |

| Lesson 3 - Basic Verilog simulation                     |

| Lesson 4 - Mixed VHDL/Verilog simulation                |

| Lesson 5 - Debugging a VHDL design                      |

| Lesson 6 - Finding names and values                     |

| Lesson 7 - Using the Wave window                        |

| Lesson 8 - Simulating with the Performance AnalyzerT-65 |

| Lesson 9 - Simulating with Code Coverage                |

| Lesson 10 - Comparing waveforms                         |

| Lesson 11 - Debugging with the Dataflow windowT-109     |

| Lesson 12 - Running a batch-mode simulationT-125        |

| Lesson 13 - Executing commands at load timeT-129        |

| Lesson 14 - Tcl/Tk and ModelSimT-131                    |

| License AgreementT-145                                  |

| Index                                                   |

## Introduction

## Chapter contents

| Software versions               |  |  |   |   |  | . T-6 |

|---------------------------------|--|--|---|---|--|-------|

| ModelSim's graphic interface.   |  |  |   | • |  | . T-6 |

| Standards supported             |  |  |   | • |  | . T-6 |

| Assumptions                     |  |  |   | • |  | . T-7 |

| Where to find our documentation |  |  |   |   |  | . T-8 |

| Technical support and updates.  |  |  |   | • |  | . T-9 |

| Before you begin                |  |  | • |   |  | . T-9 |

#### Software versions

This documentation was written to support ModelSim SE 5.7e for UNIX and Microsoft Windows 98/Me/NT/2000/XP. If the ModelSim software you are using is a later release, check the README file that accompanied the software. Any supplemental information will be there.

Although this document covers both VHDL and Verilog simulation, you will find it a useful reference even if your design work is limited to a single HDL.

## ModelSim's graphic interface

While your operating system interface provides the window-management frame, ModelSim controls all internal-window features including menus, buttons, and scroll bars. The resulting simulator interface remains consistent within these operating systems:

- SPARCstation with OpenWindows, OSF/Motif, or CDE

- IBM RISC System/6000 with OSF/Motif

- Hewlett-Packard HP 9000 Series 700 with HP VUE, OSF/Motif, or CDE

- Linux (Red Hat v. 6, 7 or later) with KDE or GNOME

- Microsoft Windows 98/Me/NT/2000/XP

Because ModelSim's graphic interface is based on Tcl/Tk, you also have the tools to build your own simulation environment. Easily accessible preference variables and configuration commands, simulator preference variables, and graphic interface commands give you control over the use and placement of windows, menus, menu options and buttons.

## Standards supported

ModelSim VHDL supports both the IEEE 1076-1987 and 1076-1993 VHDL, the 1164-1993 *Standard Multivalue Logic System for VHDL Interoperability*, and the 1076.2-1996 *Standard VHDL Mathematical Packages* standards. Any design developed with ModelSim will be compatible with any other VHDL system that is compliant with either IEEE Standard 1076-1987 or 1076-1993.

ModelSim Verilog is based on IEEE Std 1364-1995 and a partial implementation of 1364-2001 (see /<install\_dir>/modeltech/docs/technotes/vlog\_2001.note for implementation details) Standard Hardware Description Language. The Open Verilog International Verilog LRM version 2.0 is also applicable to a large extent. Both PLI (Programming Language Interface) and VCD (Value Change Dump) are supported for ModelSim PE and SE users.

In addition, all products support SDF 1.0 through 3.0, VITAL 2.2b, VITAL'95 – IEEE 1076.4-1995, and VITAL 2000 – IEEE 1076.4-2000.

## **Assumptions**

We assume that you are familiar with the use of your operating system. You should be familiar with the window management functions of your graphic interface: either OpenWindows, OSF/Motif, CDE, KDE, GNOME, or Microsoft Windows 98/Me/NT/2000/XP.

We also assume that you have a working knowledge of VHDL and Verilog. Although ModelSim is an excellent tool to use while learning HDL concepts and practices, this document is not written to support that goal.

## Where to find our documentation

ModelSim documentation is available from our website at <a href="https://www.model.com/support/documentation.asp">www.model.com/support/documentation.asp</a> or in the following formats and locations:

| Document                                            | Format    | How to get it                                                                                                                                               |  |  |  |  |  |  |

|-----------------------------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Start Here for ModelSim SE                          | paper     | shipped with ModelSim                                                                                                                                       |  |  |  |  |  |  |

| (installation & support reference)                  | PDF, HTML | select <b>Main window &gt; Help &gt; SE Documentation</b> ; also available from the Support page of our web site: <a href="www.model.com">www.model.com</a> |  |  |  |  |  |  |

| ModelSim SE Quick Guide                             | paper     | shipped with ModelSim                                                                                                                                       |  |  |  |  |  |  |

| (command and feature quick-reference)               | PDF       | select <b>Main window &gt; Help &gt; SE Documentation</b> , also available from the Support page of our web site: <a href="www.model.com">www.model.com</a> |  |  |  |  |  |  |

| ModelSim SE Tutorial                                | PDF, HTML | select <b>Main window &gt; Help &gt; SE Documentation</b> ; also available from the Support page of our web site: <a href="www.model.com">www.model.com</a> |  |  |  |  |  |  |

| ModelSim SE User's<br>Manual                        | PDF, HTML | select Main window > Help > SE Documentation                                                                                                                |  |  |  |  |  |  |

| ModelSim SE Command<br>Reference                    | PDF, HTML | select Main window > Help > SE Documentation                                                                                                                |  |  |  |  |  |  |

| ModelSim Foreign<br>Language Interface<br>Reference | PDF, HTML | select Main window > Help > SE Documentation                                                                                                                |  |  |  |  |  |  |

| Std_DevelopersKit User's                            | PDF       | www.model.com/support/pdf/sdk_um.pdf                                                                                                                        |  |  |  |  |  |  |

| Manual                                              |           | The Standard Developer's Kit is for use with Mentor Graphics QuickHDL.                                                                                      |  |  |  |  |  |  |

| ModelSim Command Help                               | ASCII     | type help [command name] at the prompt in the Main window                                                                                                   |  |  |  |  |  |  |

| Error message help                                  | ASCII     | type verror <msgnum> at the prompt in the Main window or at a shell prompt</msgnum>                                                                         |  |  |  |  |  |  |

| Tcl Man Pages (Tcl manual)                          | HTML      | select <b>Main window &gt; Help &gt; Tcl Man Pages</b> , or find contents.htm in \modeltech\docs\tcl_help_html                                              |  |  |  |  |  |  |

| application notes                                   | HTML      | www.model.com/resources/techdocs.asp                                                                                                                        |  |  |  |  |  |  |

| frequently asked questions                          | HTML      | www.model.com/resources/faqs.asp                                                                                                                            |  |  |  |  |  |  |

| tech notes                                          | ASCII     | select <b>Main window &gt; Help &gt; Technotes</b> , or located in the \modeltech\docs\technotes directory                                                  |  |  |  |  |  |  |

## **Technical support and updates**

The Model Technology web site includes links to support, software updates, and many other information sources for both Model Technology and Mentor Graphics customers.

#### Support

Online and email technical support options, maintenance renewal, and links to international support contacts: www.model.com/support/default.asp

#### **Updates**

Access to the most current version of ModelSim: www.model.com/products/release.asp

#### Latest version email

Place your name on our list for email notification of news and updates: www.model.com/support/register\_news\_list.asp

## Before you begin

Preparation for some of the lessons leaves certain details up to you. You will decide the best way to create directories, copy files and execute programs within your operating system. (When you are operating the simulator within ModelSim's GUI, the interface is consistent for all platforms.)

Additional details for VHDL, Verilog, and mixed VHDL/Verilog simulation can be found in the *ModelSim User's Manual* and *Command Reference*. (See "Where to find our documentation" (T-8).)

Examples show Windows path separators - use separators appropriate for your operating system when trying the examples.

### Command, button, and menu equivalents

Many of the lesson steps are accomplished by a button or menu selection. When appropriate, VSIM command line (PROMPT:) or menu (MENU:) equivalents for these selections are shown in parentheses within the step. This example shows three options to the **run -all** command, a button, prompt command, and a menu selection.

(PROMPT: run -all) (MENU: Simulate > Run > Run -All)

#### Drag and drop

Drag and drop allows you to copy and move signals among windows. If drag and drop applies to a lesson step, it is noted in a fashion similar to MENUS and PROMPTS with: DRAG&DROP.

#### **Command history**

As you work on the lessons, keep an eye on the Main transcript window. The commands invoked by buttons and menu selections are echoed there. You can scroll through the command history with the up and down arrow keys, or the command history may be reviewed with several shortcuts at the ModelSim/VSIM prompt.

| Shortcut        | Description                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| click on prompt | left-click once on a previous ModelSim or VSIM prompt in the transcript to copy the command typed at that prompt to the active cursor |

| his or history  | shows the last few commands (up to 50 are kept)                                                                                       |

#### Reusing commands from the Main transcript

ModelSim's Main transcript can be saved, and the resulting file used as a DO (macro) file to replay the transcribed commands. You can save the transcript at any time before or during simulation. You have the option of clearing the transcript (File > Transcript > Clear Transcript) if you don't want to save the entire command history.

To save the contents of the transcript select **File > Transcript > Save Transcript As** from the Main menu.

Replay the saved transcript with the **do** command:

```

do <do file name>

```

For example, if you saved a series of compiler commands as *mycompile.do* (the .do extension is optional), you could recompile with one command:

```

do mycompile.do

```

**Note:** Neither the prompt nor the Return that ends a command line are shown in the examples.

## **Lesson 1 - Creating a Project**

## The goals for this lesson are:

· Create a project

A project is a collection entity for an HDL design under specification or test. Projects ease interaction with the tool and are useful for organizing files and specifying simulation settings. At a minimum, projects have a work library and a session state that is stored in a .mpf file. A project may also consist of:

- HDL source files or references to source files

- other files such as READMEs or other project documentation

- local libraries

- · references to global libraries

For more information about using project files, see the ModelSim User's Manual.

## Creating a project

1 Start ModelSim with one of the following:

**for UNIX** at the shell prompt:

vsim

**for Windows** - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

Note: If you didn't add ModelSim to your search path during installation, you will have to include the full path when you type this command at a DOS prompt.

Upon opening ModelSim for the first time, you will see the **Welcome to ModelSim** dialog. (If this screen is not available, you can display it by selecting **Help > Welcome Menu** from the Main window.)

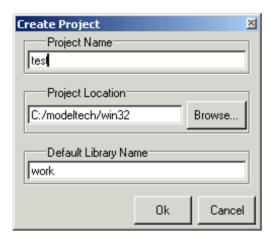

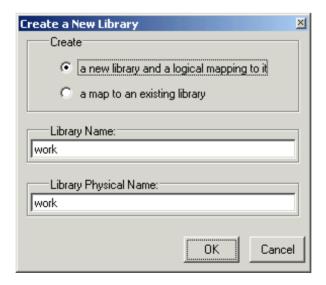

2 Select Create a Project from the Welcome dialog, or File > New > Project (Main window). In the Create Project dialog, enter "test" as the Project Name and select a

directory where the project file will be stored. Leave the Default Library Name set to "work."

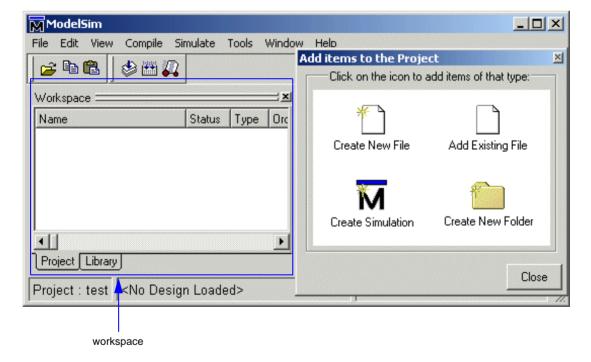

Upon selecting OK, you will see a blank Project tab in the workspace area of the Main window and the **Add Items to the Project** dialog.

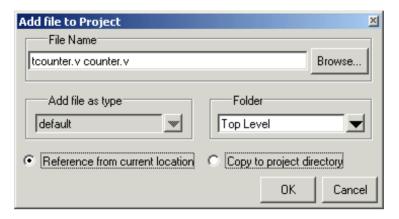

3 The next step is to add the files that contain your design units. Click **Add Existing File** in the **Add items to the Project** dialog. For this exercise, we'll add two Verilog files. Click the **Browse** button in the **Add file to Project** dialog and open the examples directory in your ModelSim installation. Select *tcounter.v.* and *counter.v.* Select **Reference from current location** and then click OK. Close the **Add items to the Project** dialog.

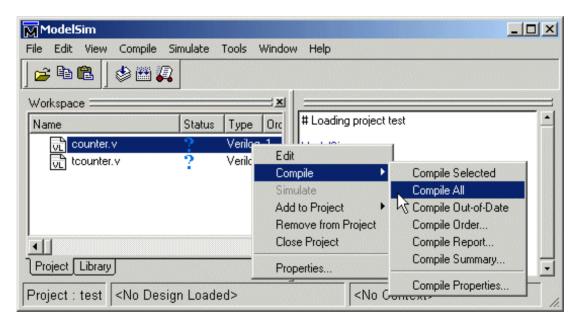

4 Click your right mouse button (2nd button in Windows; 3rd button in UNIX) in the Project page and select **Compile > Compile All**.

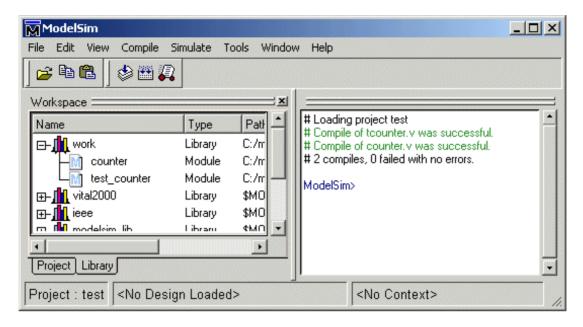

**5** The two files are compiled. Click on the Library tab and expand the *work* library by clicking the "+" icon. You'll see the compiled design units listed.

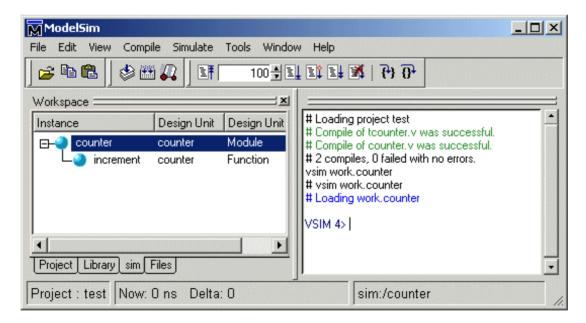

6 The last step in this exercise is to load one of the design units. Double-click *counter* on the Library page. You'll see a new page appear in the Workspace that displays the structure of the *counter* design unit.

At this point, you would generally run the simulation and analyze or debug your design. We'll do just that in the upcoming lessons. For now, let's wrap up by ending the simulation and closing the project. Select **Simulate > End Simulation** and confirm that you want to

quit simulating. Next, select **File > Close > Project** and confirm that you want to close the project.

Note that a *test.mpf* file has been created in your working directory. This file contains information about the project *test* that you just created. You can open this project in future sessions by selecting **File > Open > Project**.

## **Lesson 2 - Basic VHDL simulation**

## The goals for this lesson are:

- Create a library and compile a VHDL file

- Load a design

- Learn about the basic ModelSim windows, mouse, and menu conventions

- Force the value of a signal

- Run ModelSim using the **run** command

- Set a breakpoint

- Single-step through a simulation run

The project feature covered in Lesson 1 executes several actions automatically such as creating and mapping work libraries. In this lesson we will go through the entire process so you get a feel for how ModelSim really works.

## Compiling the design

1 Start by creating a new directory for this exercise (in case other users will be working with these lessons). Create the directory, then copy all of the VHDL (.vhd) files from \<install\_dir>\modeltech\examples to the new directory.

Make sure the new directory is the current directory. Do this by invoking ModelSim from the new directory or by selecting **File > Change Directory** (Main window).

**2** Start ModelSim with one of the following:

**for UNIX** at the shell prompt:

vsim

**for Windows** - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

Note: If you didn't add ModelSim to your search path during installation, you will have to include the full path when you type this command at a DOS prompt.

Click **Close** if the Welcome dialog appears.

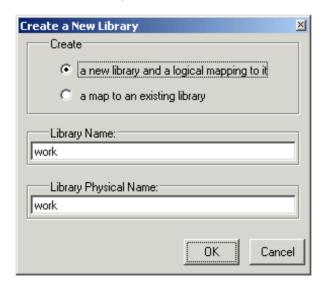

Before you compile any HDL code, you'll need a design library to hold the compilation results. To create a new design library, make this menu selection in the Main window: File > New > Library.

(PROMPT: vlib work vmap work work)

Make sure **Create:** a new library and a logical mapping to it is selected. Type "work" in the Library Name field and then select **OK**.

This creates a subdirectory named *work* - your design library - within the current directory. ModelSim saves a special file named *\_info* in the subdirectory.

- Note: Do not create a Library directory using UNIX or Windows commands, because the \_info file will not be created. Always use the File menu or the vlib command from either the ModelSim or UNIX/DOS prompt.

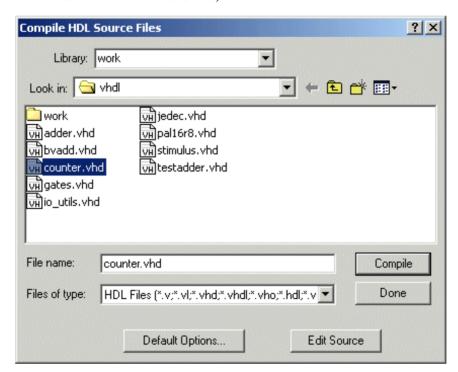

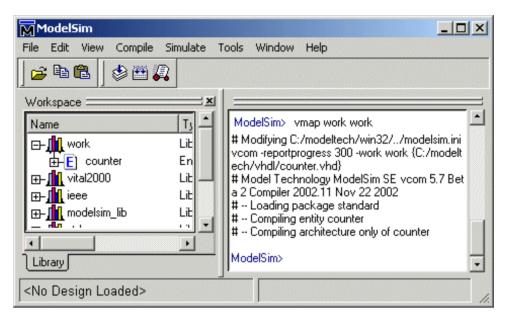

- 4 Compile the file *counter.vhd* into the new library by selecting **Compile > Compile**.

(PROMPT: vcom counter.vhd)

This opens the **Compile HDL Source Files** dialog. (You won't see this dialog if you invoke vcom from the command line.)

Complete the compilation by selecting *counter.vhd* from the file list and clicking **Compile**. Select **Done** when you are finished.

You can compile multiple files in one session from the file list. Individually select and compile the files in the order required by your design.

Note that you can have ModelSim determine the compile order. See "Auto-generating compile order" in the Project chapter of the *ModelSim User's Manual* for details.

## Loading the design

1 In the Library tab of the Main window Workspace, click the "+" sign next to the 'work' library to see the *counter* design unit.

Double-click counter to load the design unit.

2 Next, select **View > All Windows** from the Main window menu to open all ModelSim windows.

(PROMPT: view \*)

For descriptions of the windows, consult the *ModelSim User's Manual*.

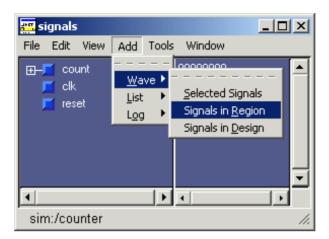

3 Next let's add top-level signals to the Wave window by selecting **Add > Wave > Signals in Region** from the Signals window menu.

(PROMPT: add wave /counter/\*)

## Running the simulation

We will start the simulation by applying stimulus to the clock input.

1 Click in the Main window and enter the following command at the VSIM prompt:

```

force clk 1 50, 0 100 -repeat 100

```

(Signals MENU: Edit > Clock)

ModelSim interprets this **force** command as follows:

- force clk to the value 1 at 50 ns after the current time

- then to 0 at 100 ns after the current time

- repeat this cycle every 100 ns

- 2 Now you will exercise two different **Run** functions from the toolbar buttons on either the Main or Wave window. (The **Run** functions are identical in the Main and Wave windows.) Select the **Run** button first. When the run is complete, select **Run -All**.

Run. This causes the simulation to run and then stop after 100 ns.

(PROMPT: run 100) (Main MENU: Simulate > Run > Run 100ns)

**Run -All**. This causes the simulator to run forever. To stop the run, go on to the next step.

(PROMPT: run -all) (Main MENU: Simulate > Run > Run -All)

3 Select the **Break** button on either the Main or Wave window toolbar to interrupt the run. The simulator will stop running as soon as it gets to an acceptable stopping point.

(Main MENU: Simulate > Break)

The arrow in the Source window points to the next HDL statement to be executed. (If the simulator is not evaluating a process at the time the Break occurs, no arrow will be displayed in the Source window.)

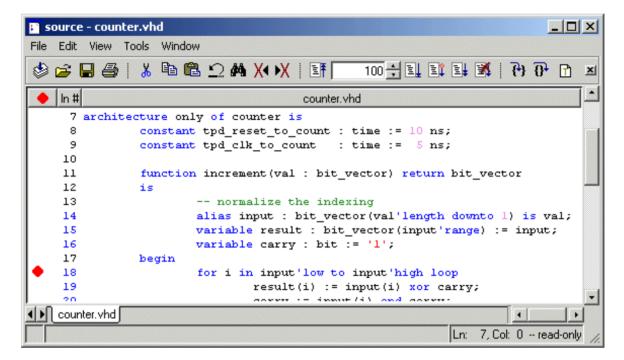

4 Next, you will set a breakpoint in the function on line 18. Scroll the Source window until line 18 is visible. Click on or near line number 18 to set the breakpoint.

You should see a red dot next to the line number where the breakpoint is set. The breakpoint can be toggled between enabled and disabled by clicking it. When a breakpoint is disabled, the dot appears open. To delete the breakpoint, click the line number with your right mouse button and select Remove Breakpoint 18.

(PROMPT: bp counter.vhd 18)

- **Note:** Breakpoints can be set only on lines with blue line numbers.

- 5 Select the **Continue Run** button to resume the run that you interrupted. ModelSim will hit the breakpoint, as shown by an arrow in the Source window and by a Break message in the Main window.

(PROMPT: run -continue) (MENU: Simulate > Run > Continue)

6 Click the **Step** button in the Main or Source window several times to single-step through the simulation. Notice that the values change in the Variables window (you may need to expand the Variables window).

(PROMPT: step) (MENU: Simulate > Run > Step)

7 This concludes the basic VHDL simulation tutorial. When you're done, quit the simulator by entering the command:

quit -force

This command exits ModelSim without asking for confirmation.

## **Lesson 3 - Basic Verilog simulation**

## The goals for this lesson are:

- Compile a Verilog design

- View signals in the design

- Examine the hierarchy of the design

- Simulate the design

- Change the default run length

- Set a breakpoint

The project feature covered in Lesson 1 executes several actions automatically such as creating and mapping work libraries. In this lesson we will go through the entire process so you get a feel for how ModelSim really works.

## Compiling the design

1 Start by creating a new directory for this exercise (in case other users will be working with these lessons). Create the directory, then copy all of the Verilog (.v) files from \<install\_dir>\modeltech\examples to the new directory.

Make sure the new directory is the current directory. Do this by invoking ModelSim from the new directory or by selecting **File > Change Directory** (Main window).

**2** Start ModelSim with one of the following:

**for UNIX** at the shell prompt:

vsim

**for Windows** - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

Note: If you didn't add ModelSim to your search path during installation, you will have to include the full path when you type this command at a DOS prompt.

Click **Close** if the Welcome dialog appears.

Before you compile any HDL code, you'll need a design library to hold the compilation results. To create a new design library, make this menu selection in the Main window: File > New > Library.

(PROMPT: vlib work vmap work work)

Make sure **Create: a new library and a logical mapping to it** is selected. Type "work" in the Library Name field and then select **OK**.

This creates a subdirectory named *work* - your design library - within the current directory. ModelSim saves a special file named *\_info* in the subdirectory.

Note: Do not create a Library directory using UNIX or Windows commands, because the \_info file will not be created. Always use the File menu or the vlib command from either the ModelSim or UNIX/DOS prompt.

In the next step you'll compile the Verilog design. The example design consists of two Verilog source files, each containing a unique module. The file *counter.v* contains a module called **counter**, which implements a simple 8-bit binary up-counter. The other file, *tcounter.v*, is a testbench module (**test\_counter**) used to verify **counter**.

Under simulation you will see that these two files are configured hierarchically with a single instance (instance name **dut**) of module **counter** instantiated by the testbench. You'll get a chance to look at the structure of this code later. For now, you need to compile both files into the **work** design library.

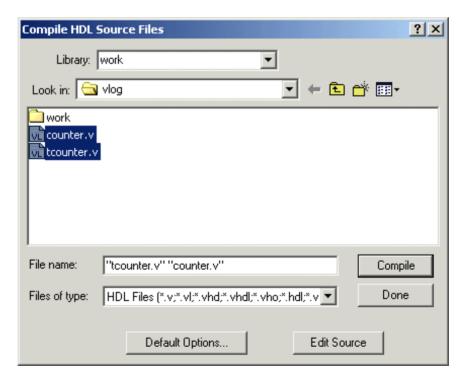

4 Compile the *counter.v*, and *tcounter.v* files into the **work** library by selecting **Compile** > **Compile** from the Main window menu.

This opens the Compile HDL Source Files dialog.

Select *counter.v* and *tcounter.v* (use Ctrl + click) and then choose **Compile** and then **Done**.

Note: The order in which you compile the two Verilog modules is not important (other than the source-code dependencies created by compiler directives). This may again seem strange to Verilog-XL users who understand the possible problems of interface checking between design units, or compiler directive inheritance. ModelSim defers such checks until the design is loaded. So it doesn't matter here if you choose to compile *counter.v* before or after *tcounter.v*.

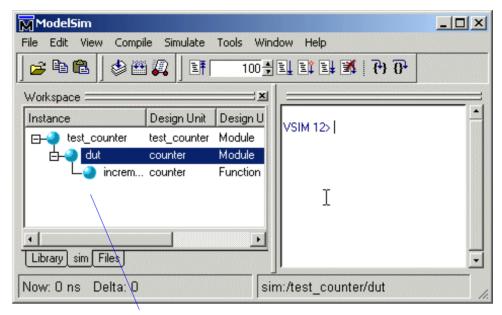

## Loading the design

1 In the Library tab of the Main window Workspace, click the "+" sign next to the 'work' library to see the *counter* and *test\_counter* design units.

Double-click *test\_counter* to load the design unit.

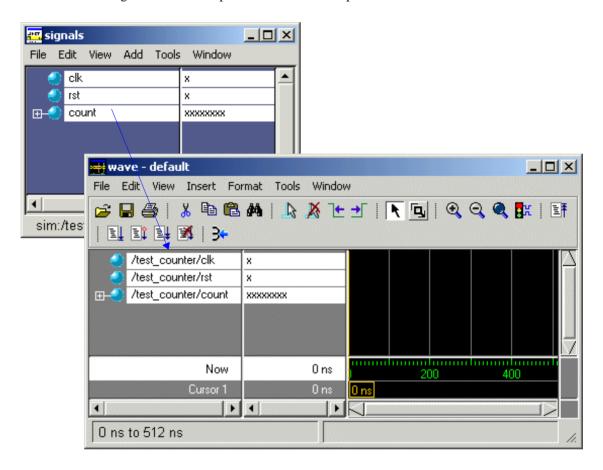

**2** Bring up the Signals, Source, and Wave windows by entering the following command at the VSIM prompt within the Main window:

```

view signals source wave

(Main MENU: View > <window name>)

```

3 Now let's add signals to the Wave window with ModelSim's drag and drop feature. In the Signals window, select **Edit** > **Select All** to select the three signals. Drag the signals to either the pathname or the values pane of the Wave window.

HDL items can also be copied from one window to another (or within the Wave and List windows) with the **Edit > Copy** and **Edit > Paste** menu selections.

**4** You may have noticed when you loaded the design in Step 1 that a new tab appeared in the Workspace area of the Main window.

Structure pane

The Structure tab shows the hierarchical structure of the design. By default, only the top level of the hierarchy is expanded. You can navigate within the hierarchy by clicking on any line with a "+" (expand) or "-" (contract) symbol. The same navigation technique works anywhere you find these symbols within ModelSim.

By clicking the "+" next to *dut* you can see all three hierarchical levels: *test\_counter*, *dut* (counter), and a function called *increment*. (If *test\_counter* is not displayed, you simulated *counter* instead of *test\_counter*.)

5 Click on *increment* and notice how other ModelSim windows are automatically updated as appropriate. Specifically, the Source window displays the Verilog code at the hierarchical level you selected in the Structure tab, and the Signals window displays the appropriate signals. Using the Structure tab in this way is analogous to scoping commands in interpreted Verilog simulators.

For now, make sure the *test\_counter* module is showing in the Source window by clicking on the top line in the Structure tab.

## Running the simulation

Now you will exercise different Run functions from the toolbar.

1 Select the **Run** button on the Main window toolbar. This causes the simulation to run and then stop after 100 ns (the default simulation length).

(PROMPT: run) (MENU: Simulate > Run > Run 100 ns)

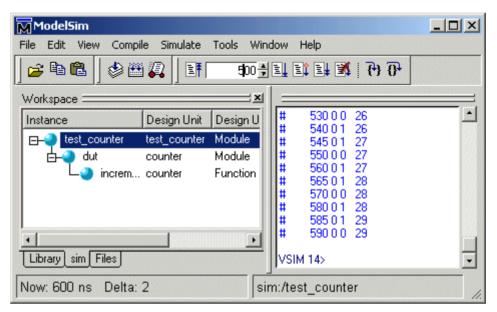

2 Next change the run length to 500 on the **Run Length** selector and select the **Run** button again.

Now the simulation has run for a total of 600ns (the default 100ns plus the 500 you just asked for). The status bar at the bottom of the Main window displays this information.

The last command you executed (**run 500**) caused the simulation to advance for 500ns. You can also advance simulation to a specific time. Type:

run @ 3000

This advances the simulation to time 3000ns. Note that the simulation actually ran for an additional 2400ns (3000 - 600).

4 Now select the **Run -All** button from the Main window toolbar. This causes the simulator to run until the stop statement in *tcounter.v*.

(PROMPT: run -all) (MENU: Simulate > Run > Run -All)

You can also use the **Break** button to interrupt a run.

(MENU: Simulate > Break)

## Debugging

Next we'll take a brief look at an interactive debugging feature of the ModelSim environment.

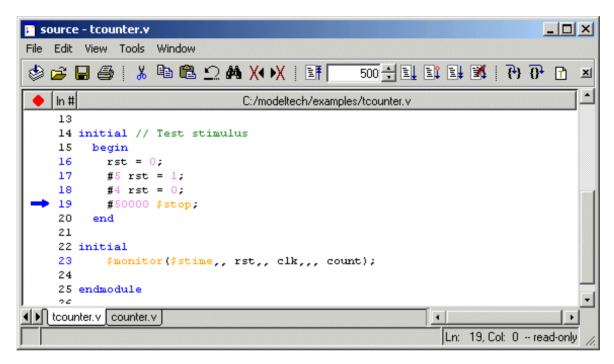

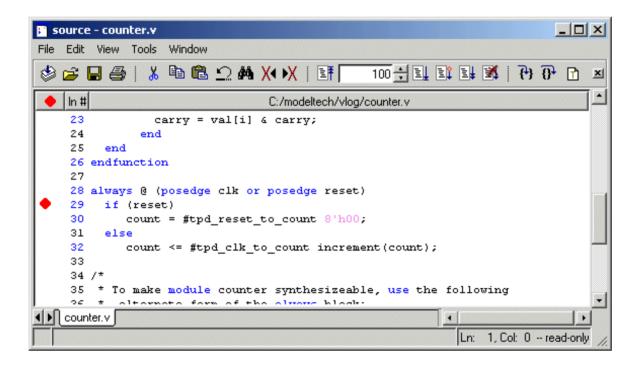

1 Let's set a breakpoint at line 29 in the *counter.v* file (which contains a call to the Verilog function increment). To do this, select *dut* in the Structure tab of the Workspace. Move the cursor to the Source window and scroll the window to display line 29. Click on or to the left of the 29 to set a breakpoint. You should see a red dot next to the line number where the breakpoint is set.

The breakpoint can be toggled between enabled and disabled by clicking it. When a breakpoint is disabled, the dot appears open. To delete the breakpoint, click the line number with your right mouse button and select **Remove Breakpoint 29**.

**Note:** Breakpoints can be set only on lines with blue line numbers.

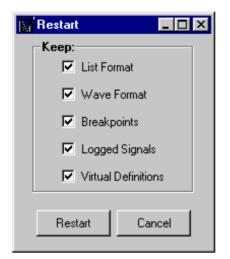

2 Select the Restart button to reload the design elements and reset the simulation time to zero.

(Main MENU: Simulate > Run > Restart) (PROMPT: restart)

T-35

Make sure all items in the Restart dialog box are selected, then click Restart.

3 Select the **Run -All** button to re-start the simulation run.

(PROMPT: run -all) (Main MENU: Simulate > Run > Run -All)

When the simulation hits the breakpoint, it stops running, highlights the line with an arrow in the Source window, and issues a Break message in the Main window.

- **4** When a breakpoint is reached, typically you will want to know one or more signal values. You have several options for checking values:

- look at the values shown in the Signals window

- hover your mouse pointer over the *count* variable in the Source window and a "balloon" will pop up with the value

- select the count variable in the Source window, right-click it, and select Examine from the context menu;

- use the examine command to output the value to the Main window transcript:

examine count

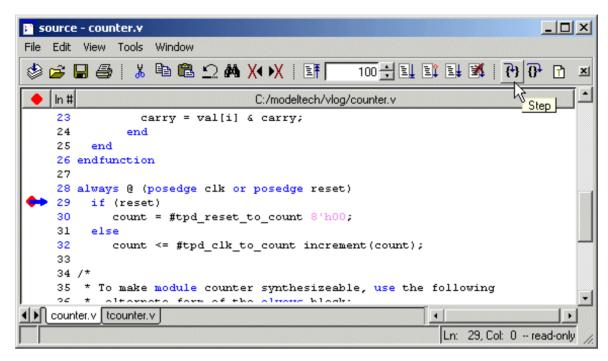

**5** Let's move through the Verilog source functions with ModelSim's Step command. Click **Step** on the toolbar.

This command single-steps the debugger.

**6** Experiment by yourself for awhile. Set and clear breakpoints and use the Step, Step Over, and Continue Run commands until you feel comfortable with their operation. When you're done, quit the simulator by entering the command:

```

quit -force

```

# **Lesson 4 - Mixed VHDL/Verilog simulation**

# The goals for this lesson are:

- Compile multiple VHDL and Verilog files

- Simulate a mixed VHDL and Verilog design

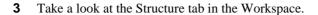

- View the design in the Structure tab

- View the HDL source code in the Source window

- Note: You must be using ModelSim SE/PLUS or ModelSim SE/MIXED to do this lesson.

## Compiling the design

1 Start by creating a new directory for this exercise. Create the directory, then copy the VHDL and Verilog example files to the directory:

```

<install_dir>\modeltech\examples\mixedHDL\*.vhd

<install_dir>\modeltech\examples\mixedHDL\*.v

```

Make sure the new directory is the current directory. Do this by invoking ModelSim from the new directory or by using the **File > Change Directory** command from the ModelSim Main window.

2 Start ModelSim with one of the following:

for UNIX at the shell prompt:

vsim

**for Windows** - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

Note: If you didn't add ModelSim to your search path during installation, you will have to include the full path when you type this command at a DOS prompt.

Click **Close** if the Welcome dialog appears.

**3** Before you compile any HDL code, you'll need a design library to hold the compilation results. To create a new design library, make this menu selection in the Main window: **File > New > Library**.

(PROMPT: vlib work vmap work work)

Make sure **Create: a new library and a logical mapping to it** is selected. Type "work" in the Library Name field and then select **OK**.

This creates a subdirectory named *work* - your design library - within the current directory. ModelSim saves a special file named *\_info* in the subdirectory.

- Note: Do not create a Library directory using UNIX or Windows commands, because the *\_info* file will not be created. Always use the File menu or the **vlib** command from either the ModelSim or UNIX/DOS prompt.

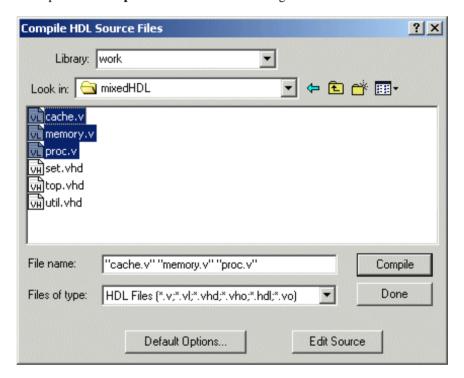

- **4** Compile the HDL files by selecting **Compile > Compile** from the menu:

(PROMPT: vlog cache.v memory.v proc.v)

(PROMPT: vcom util.vhd set.vhd top.vhd)

This opens the Compile HDL Source Files dialog.

A group of Verilog files may be compiled in any order. However, in a mixed VHDL/Verilog design, the Verilog files must be compiled before the VHDL files.

Compile the Verilog source by double-clicking each of these Verilog files in the file list (this invokes the Verilog compiler, **vlog**):

- cache.v

- memory.v

- proc.v

**5** Depending on the design, the compile order of VHDL files can be very specific. In the case of this lesson, the file *top.vhd* must be compiled last.

Stay in the **Compile HDL Source Files** dialog and double-click the VHDL files in this order (this invokes the VHDL compiler, **vcom**):

- util.vhd

- set.vhd

- top.vhd

- 6 Click **Done** to dismiss the dialog.

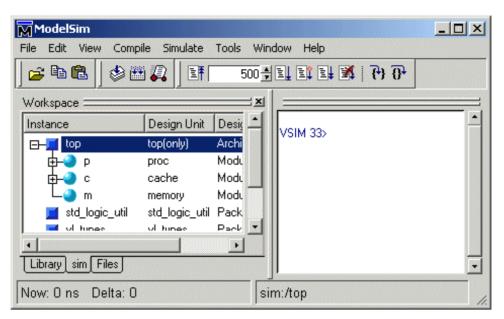

## Loading the design

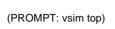

1 Load the design by selecting **Simulate > Simulate** from the menu.

The Simulate dialog appears. Click the "+" sign next to 'work' to see the design units. (You won't see this dialog box if you invoke **vsim** with *top* from the command line.) Select **top** and then click **OK**.

**2** From the Main menu select **View > All Windows** to open all ModelSim windows.

(PROMPT: view \*)

Notice the hierarchical mixture of VHDL and Verilog in the design. VHDL levels are indicated by a square "prefix", while Verilog levels are indicated by a circle "prefix." Try expanding (+) and contracting (-) the structure layers. You'll find Verilog modules that have been instantiated by VHDL architectures, and similar instantiations of VHDL items by Verilog.

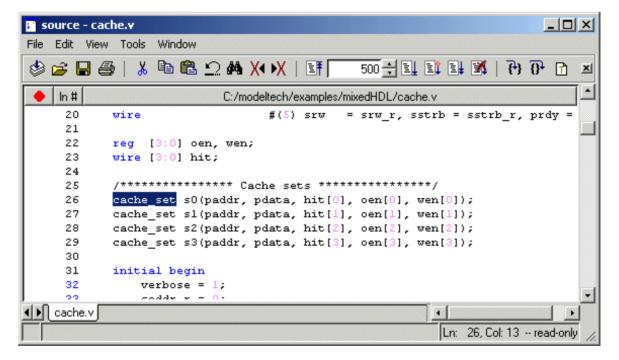

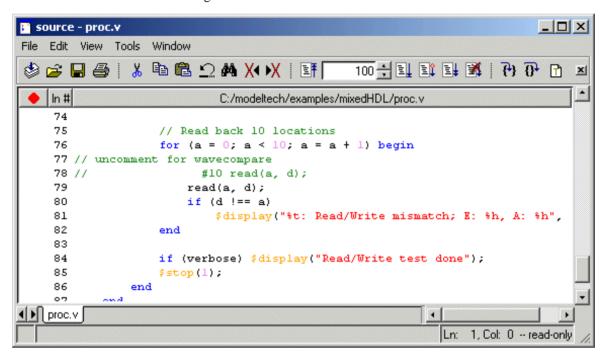

**4** In the Structure tab, click the Verilog module *c cache*. The source code for the Verilog module is now shown in the Source window.

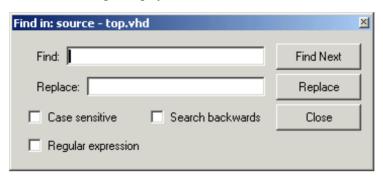

**5** We'll use ModelSim's Find function to locate the declaration of *cache\_set* within *cache.v*.

From the Source window menu select: **Edit > Find**.

The **Find in** dialog is displayed.

In the **Find:** field, type *cache\_set* and click **Find Next**. The *cache\_set* instantiations are now displayed in the Source window. (Click **Close** to dismiss the **Find in:** dialog box.)

Note that *cache\_set* is a VHDL entity instantiated within the Verilog file *cache.v*.

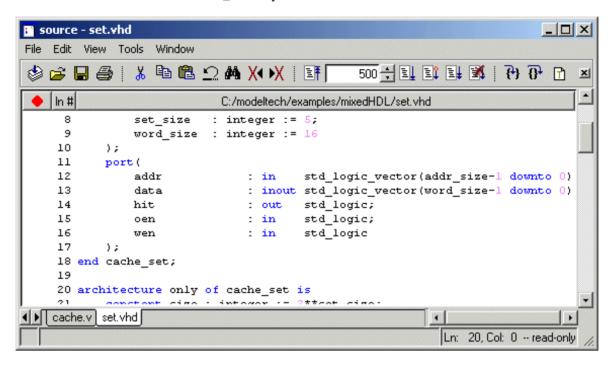

**6** Go back to the Main window, expand the *c cache* entry by clicking the "+" sign, and scroll down and click on *s0 cache\_set(only)*. The Source window shows the VHDL code for the *cache\_set* entity.

Before you quit, try experimenting with some of the commands you've learned from previous lessons – add signals to the Wave window, run the simulation, etc. Note that in this design, *clk* is already driven, so you won't need to use the **force** command.

**7** When you're ready to quit simulating, enter the command:

quit -force

# Lesson 5 - Debugging a VHDL design

## The goals for this lesson are:

- Map a logical library name to an actual library

- Recognize assertion messages in the Main window transcript

- Change the assertion break level

- Restart the simulation run using the **restart** command

- Examine composite types displayed in the Variables window

- Change the value of a variable

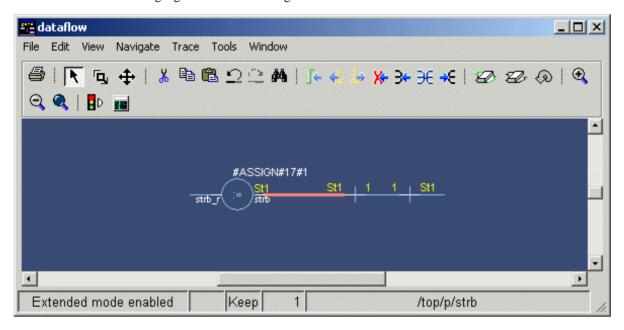

In this lesson we will debug an assertion message using the Source, Signals, and Variables windows. For another debugging lesson, see *Lesson 11 - Debugging with the Dataflow window*.

### Compiling and loading the design

- 1 Create a new directory for this exercise and copy the following VHDL (.vhd) files from \<i install\_dir>\modeltech\examples to the new directory.

- · gates.vhd

- adder.vhd

- testadder.vhd

- 2 Make sure the new directory is the current directory. Do this by invoking ModelSim from the new directory or by using the **File > Change Directory** command from the ModelSim Main window.

- **3** Start ModelSim with one of the following:

for UNIX at the shell prompt:

vsim

**for Windows** - your option - from a Windows shortcut icon, from the Start menu, or from a DOS prompt:

modelsim.exe

- Note: If you didn't add ModelSim to your search path during installation, you will have to include the full path when you type this command at a DOS prompt.

- **4** Enter the following command at the ModelSim prompt in the Main window to create a new library:

```

vlib library_2

```

**5** Map the new library to the work library using the **vmap** command:

```

vmap work library_2

```

ModelSim adds this mapping to the *modelsim.ini* file.

**6** Compile the source files into the new library by entering this command at the ModelSim prompt:

vcom -work library\_2 gates.vhd adder.vhd testadder.vhd

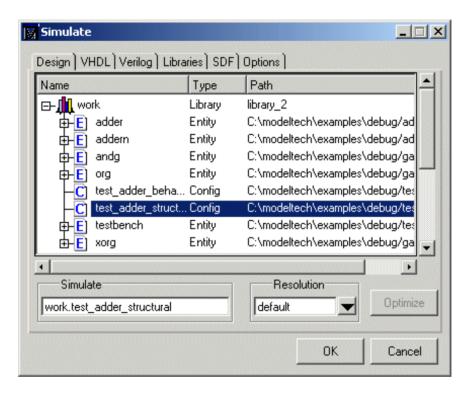

- 7 Open the Simulate dialog by selecting Simulate > Simulate. Expand the work library and increase the width of the name column by clicking and dragging on the border between the Name and Type columns.

- 8 Make sure Simulator Resolution is set to nanoseconds, select **test\_adder\_structural**, and then click **OK**.

(PROMPT: vsim -t ns work.test\_adder\_structural)

## **Running the simulation**

1 Start by opening the Process, Variables, and Signals windows using the command below. Note that you can abbreviate window names.

```

view p si v

(Main MENU: View > <window name>)

```

2 Now run the simulation for 1000 ns:

```

run 1000

```

A message in the Main window will notify you that there was an assertion error.

## **Debugging the simulation**

Let's find out what is wrong. Perform the following steps to track down the assertion message.

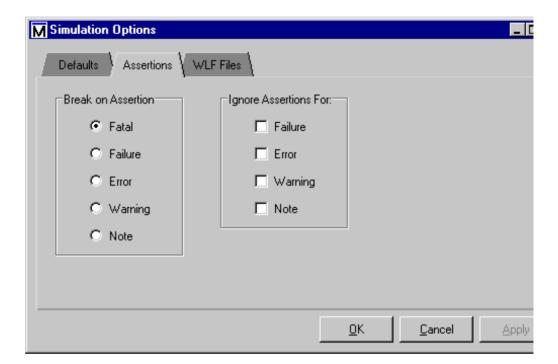

1 First, change the simulation assertion options. Select **Simulate > Simulation Options** from the Main window menu.

- 2 Select the **Assertions** tab. Change the selection for **Break on Assertion** to **Error** and click **OK**. This will cause the simulator to stop at the HDL assertion statement.

- **3** Restart the simulation using the following command:

restart -f

The -f option causes ModelSim to restart without popping up the confirmation dialog.

4 Run the simulation again for 1000 ns.

run 1000

The Source window opens automatically to show the line where the break occurred. Notice that the arrow in the Source window is pointing to the assertion statement.

```

source - testadder.vhd

File Edit View Tools

Window

100 🕂 🖺 🖺 📑

E

In#

testadder.vhd

108

4 ". Expected " 4 to string(vector.sum)

109

found error := true;

110

end if:

111

if (cout /= vector.cout) then

assert false

112

report "Cout is " & to char(cout) & ".

113

114

& "Expected value is " & to char(vector

115

found error := true;

```

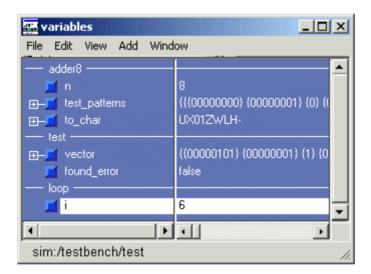

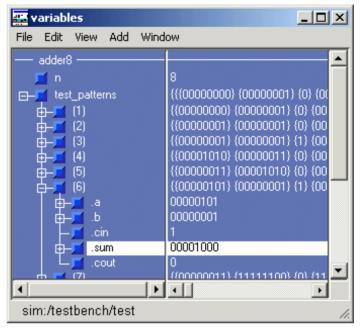

5 If you look at the Variables window now, you can see that i = 6. This indicates that the simulation stopped in the sixth iteration of the test pattern's loop.

- **6** Expand the variable named **test\_patterns** by clicking the [+]. (You may need to resize the window for a better view.)

- **7** Also expand the sixth record in the array **test\_patterns(6)**, by clicking the [+]. The Variables window should be similar to the one below.

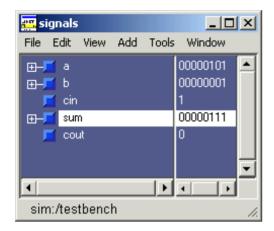

The assertion shows that the Signal **sum** does not equal the **sum** field in the Variables window. Note that the sum of the inputs **a**, **b**, and **cin** should be equal to the output **sum**. But there is an error in the test vectors. To correct this error, you need to restart the simulation and modify the initial value of the test vectors.

**8** Restart the simulation again:

restart -f

- **9** Update the Variables window by selecting the **test** process in the Process window.

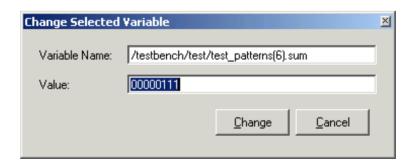

- **10** In the Variables window, expand **test\_patterns** and **test\_pattern(6)** again. Then highlight the .**sum** record by clicking on the variable name (not the box before the name) and select **Edit** > **Change** from the menu.

- 11 Change the value to **00000111** and then click **Change**. (Note that this is a temporary edit, you must use your text editor to permanently change the source code.)

- **12** Run the simulation again for 1000 ns.

```

run 1000

```

At this point, the simulation will run without errors.

```

VSIM 30> run 1000

# ** Note: Test completed with no errors.

# Time: 1 us Iteration: 0 Instance: /testbench

VSIM 31>

stbench

```

This brings you to the end of this lesson, but feel free to explore the system further. When you are ready to end the simulation session, quit ModelSim by entering the following command at the VSIM prompt:

```

quit -f

```

# **Lesson 6 - Finding names and values**

# The goals for this lesson are:

- Find items by name in tree windows

- Search for item values in the List and Wave windows

Start any of the lesson simulations to try out the Find and Search functions illustrated below.

# Finding items by name in tree windows

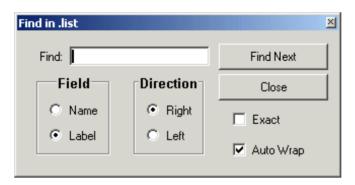

You can find HDL item names with the **Edit > Find** menu selection in these windows: Dataflow, List, Process, Signals, Source, Structure, Variables, and Wave windows.

Select **Edit** > **Find** to bring up the Find dialog box (List window version shown).

Enter an item label and Find it by searching Right or Left through the window display.

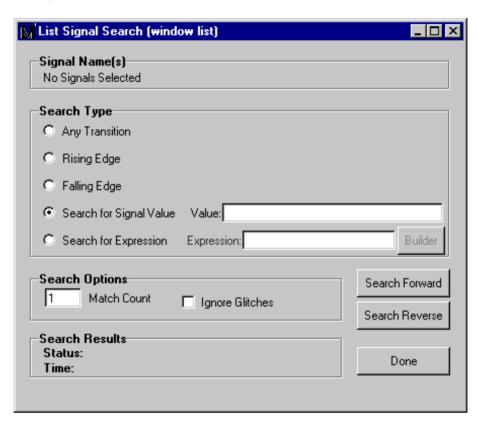

### Searching for item values in the List and Wave windows

You can search for HDL item values in the List and Wave windows. Select **Edit > Search** from the window's menu to bring up the Signal Search dialog box (List window version shown).

You can locate values for the **Signal Name(s)** shown at the top of the dialog box. The search is based on these options:

- Search Type: Any Transition

Searches for any transition in the selected signal(s).

- Search Type: Rising Edge

Searches for rising edges in the selected signal(s).

- Search Type: Falling Edge Searches for falling edges in the selected signal(s).

- Search Type: Search for Signal Value

Searches for the value specified in the Value field; the value should be formatted using VHDL or Verilog numbering conventions.

#### Search Type: Search for Expression

Searches for the expression specified in the **Expression** field evaluating to a boolean true. Activates the **Builder** button so you can use the Expression Builder if desired.

The expression may involve more than one signal but is limited to signals logged in the List or Wave window. Expressions may include constants, variables, and Tcl macros. If no expression is specified, the search will give an error. See the *ModelSim Command Reference* for more information on expression syntax.

#### • Search Options: Match Count

You can search for the nth transition or the nth match on value; **Match Count** indicates the number of transitions or matches to search.

#### • Search Options: Ignore Glitches

Ignore zero width glitches in VHDL signals and Verilog nets.

The result of your search is indicated at the bottom of the dialog box.

# **Lesson 7 - Using the Wave window**

# The goals for this lesson are:

- Practice using the Wave window time cursors.

- Practice zooming the waveform display.

- Practice using Wave window keyboard shortcuts.

- Practice combining items into a virtual object.

- Practice creating and viewing datasets.

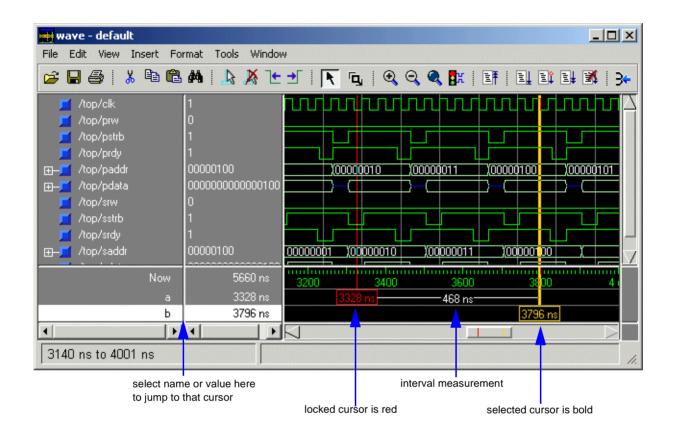

### Using time cursors in the Wave window

Any of the previous lesson simulations may be used with this part of the lesson, or use your own simulation if you wish.

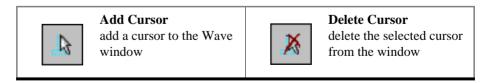

When the Wave window is first drawn, there is one cursor located at time zero. Clicking anywhere in the waveform display brings that cursor to the mouse location. You can add cursors to the waveform pane by selecting **Insert > Cursor** (or the Add Cursor button shown below). The selected cursor is drawn as a bold solid line; all other cursors are drawn with thin lines. Remove cursors by selecting them and selecting **Edit > Delete Cursor** (or the Delete Cursor button shown below).

### **Naming cursors**

By default cursors are named "Cursor <n>". To rename a cursor, click the name in the left-hand cursor pane with your right mouse button. Type a new name and press the <Enter> key on your keyboard.

#### **Locking cursors**

You can lock a cursor in position so it won't move. Click a cursor with your right-mouse button and select **Lock <cursor name>**. The cursor turns red and you can no longer move it with the mouse. As a convenience, you can hold down the <shift> key and click-and-drag the cursor. Once you let go of the cursor, it will be locked in the new position. To unlock a cursor, right-click it and select **Unlock <cursor name>**.

#### **Finding cursors**

The cursor value corresponds to the simulation time of that cursor. Choose a specific cursor view by selecting **View > Cursors** (Wave window). You can also select and scroll to a cursor by double-clicking its value in the cursor-value pane.

Alternatively, you can click a value with your right mouse button, type the value to which you want to scroll, and press the Enter key.

#### **Making cursor measurements**

Each cursor is displayed with a time box showing the precise simulation time at the bottom. When you have more than one cursor, each time box appears in a separate track at the bottom of the display. ModelSim also adds a delta measurement showing the time difference between two adjacent cursor positions.

If you click in the waveform display, the cursor closest to the mouse position is selected and then moved to the mouse position. Another way to position multiple cursors is to use the mouse in the time box tracks at the bottom of the display. Clicking anywhere in a track selects that cursor and brings it to the mouse position.

Cursors will "snap" to a waveform edge if you click or drag a cursor to within ten pixels of a waveform edge. You can set the snap distance in the Window Preferences dialog (select **Tools > Window Preferences**). You can position a cursor without snapping by dragging in the area below the waveforms.

You can also move cursors to the next transition of a signal with these toolbar buttons:

#### Find Previous Transition

locate the previous signal value change for the selected signal

#### **Find Next Transition**

locate the next signal value change for the selected signal

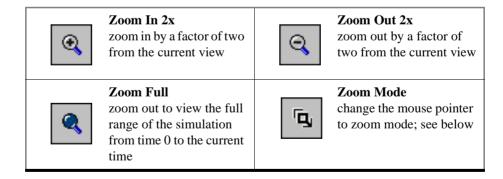

### Zooming - changing the waveform display range

Zooming lets you change the simulation range in the waveform pane. You can zoom using a context menu, toolbar buttons, mouse, keyboard, or commands.

#### Using the Zoom menu

You can access Zoom commands from the **View** menu on the toolbar or by clicking the right mouse button in the waveform pane.

The Zoom menu options include:

#### · Zoom In

Zooms in by a factor of two, increasing the resolution and decreasing the visible range horizontally. (command: .wave.tree zoomin)

#### Zoom Out

Zooms out by a factor of two, decreasing the resolution and increasing the visible range horizontally. (command: .wave.tree zoomout)

#### Zoom Full

Redraws the display to show the entire simulation from time 0 to the current simulation time. (command: .wave.tree zoomfull)

#### Zoom Last

Restores the display to where it was before the last zoom operation. (command: .wave.tree zoomlast)

#### · Zoom Range

Brings up a dialog box that allows you to enter the beginning and ending times for a range of time units to be displayed. (command: .wave.tree zoomrange)

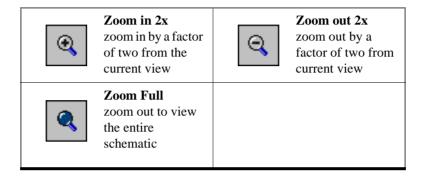

### Zooming with toolbar buttons

These zoom buttons are available on the toolbar:

### Zooming with the mouse

To zoom with the mouse, first enter zoom mode by selecting **View > Mouse Mode > Zoom Mode** (Wave window). The left mouse button (<Button-1>) then offers 3 zoom options by clicking and dragging in different directions:

• Down-Right: Zoom Area (In)

Up-Right: Zoom OutUp-Left: Zoom Fit

The zoom amount is displayed at the mouse cursor. A zoom operation must be more than 10 pixels to activate.

### **Keyboard shortcuts for zooming**

Using the following keys when the mouse cursor is within the Wave window will cause the indicated actions:

| Key                                                                  | Action                                                                                               |

|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| i I or +                                                             | zoom in                                                                                              |

| o O or -                                                             | zoom out                                                                                             |

| f or F                                                               | zoom full                                                                                            |

| l or L                                                               | zoom last                                                                                            |

| r or R                                                               | zoom range                                                                                           |

| <arrow up=""></arrow>                                                | scroll pathname, values, or waveform pane up                                                         |

| <arrow down=""></arrow>                                              | scroll pathname, values, or waveform pane down                                                       |

| <arrow left=""></arrow>                                              | scroll pathname, values, or waveform pane left                                                       |

| <arrow right=""></arrow>                                             | scroll pathname, values, or waveform pane right                                                      |

| <page up=""></page>                                                  | scroll waveform display up by page                                                                   |

| <page down=""></page>                                                | scroll waveform display down by page                                                                 |

| <control -="" arrow="" left=""></control>                            | scroll waveform display left one page                                                                |

| <control -="" arrow="" right=""></control>                           | scroll waveform display right one page                                                               |

| <tab></tab>                                                          | searches forward (right) to the next transition on the selected signal                               |

| <shift-tab></shift-tab>                                              | searches backward (left) to the previous transition on the selected signal                           |

| <control-f> (Windows)<br/><control-s> (UNIX)</control-s></control-f> | opens the find dialog box; searches within the specified field in the pathname pane for text strings |

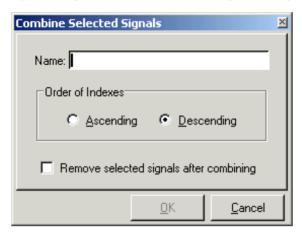

### Combining items in the Wave window

The Wave window allows you to combine signals into buses. Select **Tools > Combine Signals** to open the Combine Selected Signals dialog.

A bus is a collection of signals concatenated in a specific order to create a new virtual signal with a specific value.

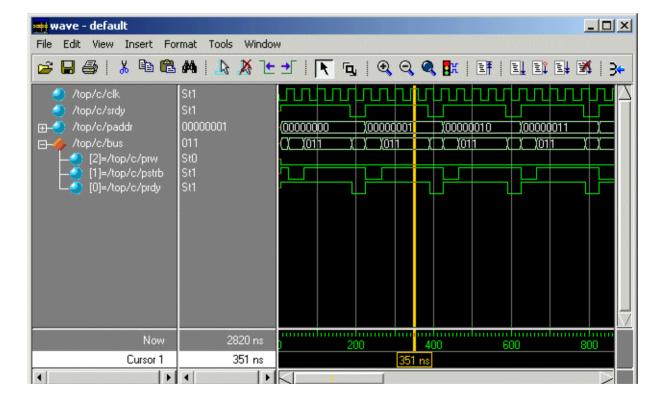

In the illustration below, three data signals have been combined to form a new bus called "bus". Notice, the new bus has a value that is made up of the values of its component signals arranged in a specific order. Virtual objects are indicated by an orange diamond.

## Creating and viewing datasets

Datasets allow you to view previous simulations or to compare simulations. To view a dataset, you must first save a ModelSim simulation to a WLF file (using the **vsim -wlf** option or **File > Save > Dataset** command). Once you have saved a WLF file, you can open it as a view-mode dataset.

In this lesson you will compare two simple Verilog designs: a structural description and an RTL description of a 4-bit, binary counter. To begin, you will simulate the structural description and save it to a WLF file. Then you will simulate the RTL version. Finally, you will open the WLF file as a dataset and compare the two simulations in the Wave window.

#### Simulating the structural version

- 1 Start by creating a new working directory, making it the current directory, and copying the files from \modeltech\examples\datasets into it.

- 2 Use the **vlib** command to create a **work** library in the current directory.

```

vlib work

(MENU: File > New > Library)

```

**3** Use the **vmap** command to map the work library to a physical directory.

```

vmap work work

```

Your *modelsim.ini* file will be updated with this mapping.

**4** Compile the structural version of the counter.

```

vlog cntr_struct.v

```

(MENU: Compile > Compile)

**5** Load the design and save the simulation to a WLF file named *struct.wlf*.

```

vsim -wlf struct.wlf work.cntr_struct

```

6 Now you will run a DO file that applies stimulus to the design, runs the simulation, and adds waves to the Wave window. Feel free to open the DO file and look at its contents.

```

do stimulus.do

```

(MENU: Tools > Execute Macro)

The waves that appear in the Wave window are saved automatically into the *struct.wlf* file.

**7** Quit the simulation.

```

quit -sim

```

(MENU: Simulate > End Simulation)

#### Simulating the RTL version

1 Compile the RTL version of the counter.

vlog cntr\_rtl.v

**2** Simulate the design.

vsim work.cntr\_rtl

(MENU: Simulate > Simulate)

**3** Run the DO file to apply stimulus to the design.

do stimulus.do

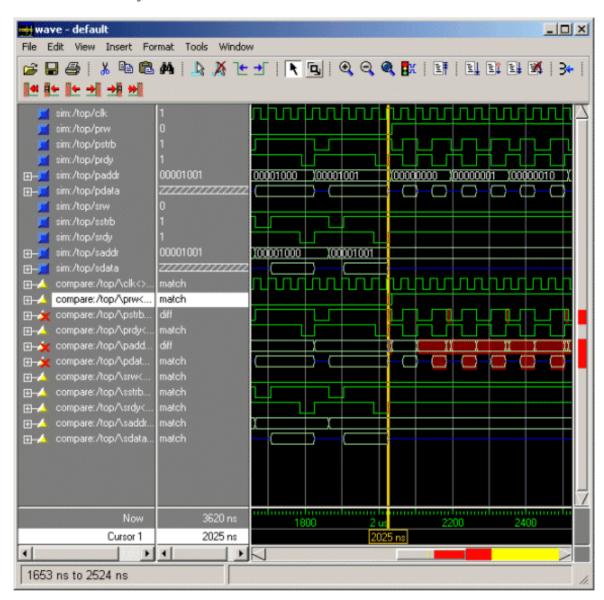

### Comparing the two designs

To compare the two simulations, we will create a second pane in the Wave window, open the *struct.wlf* file, and add the signals from the dataset to the new pane.

**1** Add a second pane to the Wave window.

Wave MENU: Insert > Window Pane

Notice that a thick, white vertical bar at the left edge of the window indicates that the new pane is active.

**2** Open *struct.wlf*.

dataset open struct.wlf

**3** Add signals for the "struct" dataset.

(Wave MENU: File > Open > Dataset)

add wave \*

Notice that the pathname prefix for the signals you just added is the dataset name "struct". The pathname prefix for the active simulation is "sim".

The results for each simulation should be the same. You can continue experimenting with the two simulations or quit the simulation.

quit -sim

(Main MENU: Simulate > End Simulation)

# **Lesson 8 - Simulating with the Performance Analyzer**

### The goals for this lesson are:

- Run a simulation with Performance Analyzer turned on

- View the Hierarchical Profile display

- Use the Performance Analyzer statistics displayed in the Hierarchical Profile to speed up simulation

The Performance Analyzer identifies the percentage of simulation time spent in each section of your code. With this information, you can identify bottlenecks and reduce simulation time by optimizing your code. Users have reported up to 75% reductions in simulation time after using the Performance Analyzer.

This lesson introduces the Performance Analyzer and shows you how to use the main Performance Analyzer commands.

Note: You must be using ModelSim SE to complete this lesson.

# Compiling and loading the design

This lesson will use an example design that contains lower-level VHDL blocks in the files *control.vhd*, *retrieve.vhd*, and *store.vhd*; and top-level block, test bench and configuration files – *ringrtl.vhd*, *testring.vhd*, and *config\_rtl.vhd*.

- 1 Start by creating a new working directory, making it the current directory, and copying the files from \modeltech\examples\profiler\ into it.

- **2** Use the **vlib** command to create a **work** library in the current directory.

```

vlib work (MENU: File > New > Library)

```

**3** Use the **vmap** command to map the work library to a physical directory.

```

vmap work work

```

Your modelsim.ini file will be updated with this mapping.

4 Compile the lower level blocks of the design.

vcom control.vhd retrieve.vhd store.vhd

**5** Compile the top-level block, testbench and configuration files.

vcom ringrtl.vhd testring.vhd config\_rtl.vhd

**6** Use the **vsim** command to load the design configuration.

vsim work.test\_bench\_rtl

(MENU: Simulate > Simulate)

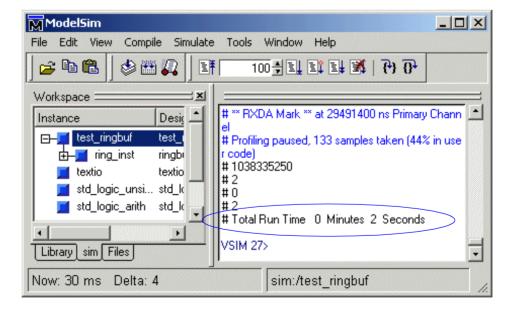

### Running the simulation

1 Turn on profiling prior to running the simulation.

profile on

(MENU: Tools > Profile > Profile On)

**2** We're going to run the simulation using a DO file that reports how long the simulation takes to run. Take a look at the commands in the *timerun.do* file. The *seconds* Tcl command is used to time the simulation.

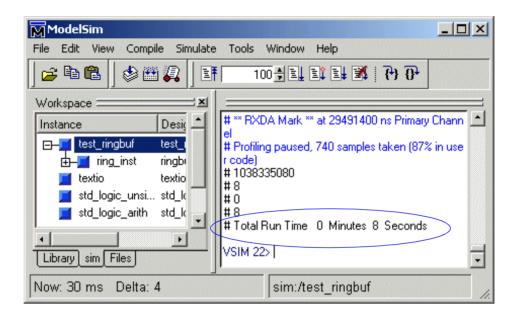

do timerun.do

Notice as the simulation runs that the status bar shows how many profile samples are being taken.

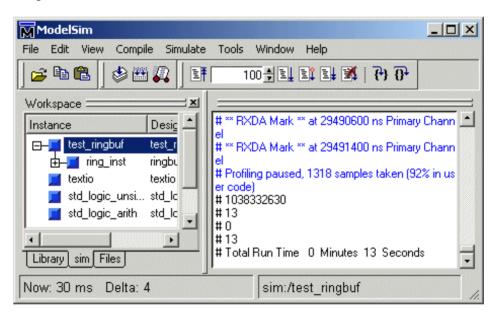

Make a note of the run time reported in the Transcript window. We'll use it later to compare how much we've increased simulation speed. (Your times may differ from those shown here due to differing system configurations.)

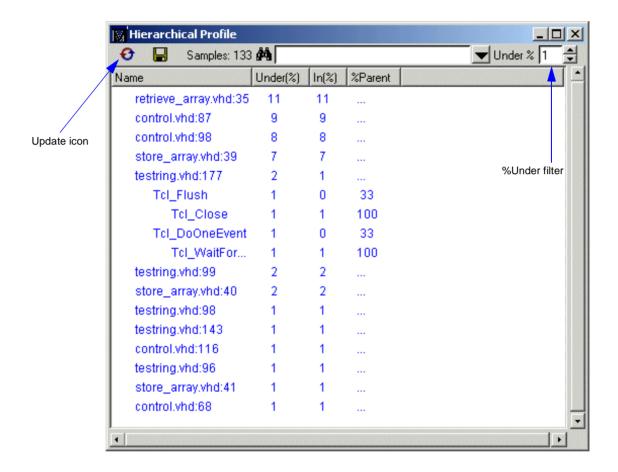

3 Display the Hierarchical Profile output.

view\_profile

(MENU: Tools > Profile > View hierarchical profile)

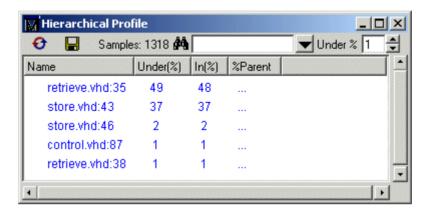

Note that two lines – *retrieve.vhd:35* and *store.vhd:43* – are taking the majority of the simulation time.

You can filter out everything below a certain percentage with the **Under %** field on the toolbar. The default value is 1%. Any usage less than 1% will not be displayed.

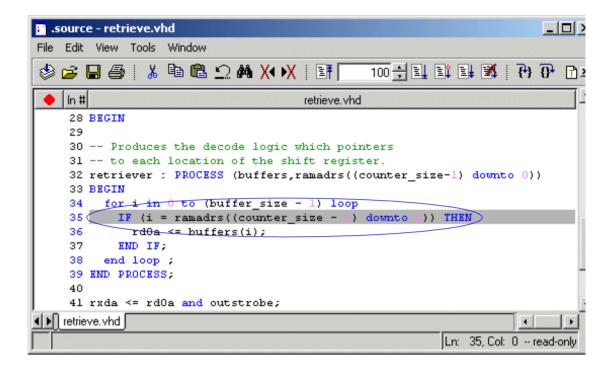

Clicking any line in the Hierarchical Profile window will open the Source window and allow you to view the relevant source code for that line. The selected line will be highlighted in the Source window as shown below. (Here, we've double-clicked *retrive.vhd:35*.)

# Speeding up the simulation

The information provided by the Performance Analyzer can be used to speed up the simulation. Click the pathname for *retrieve.vhd:35* and *store.vhd:43* and view the source code. In both cases, the source includes a loop which could have an exit.

1 Modify the loops to include exits inside the *IF* statements, or compile the following files included for that purpose – *store\_exit.vhd* and *retrieve\_exit.vhd*.

vcom retrieve\_exit.vhd store\_exit.vhd

(MENU: Compile > Compile)

**2** Compile the top level blocks and configuration files again to account for the lower level changes.

vcom ringrtl.vhd testring.vhd config\_rtl.vhd

(MENU: Compile > Compile)

**3** Reset the simulation to time zero and restart with the modified files.

restart -f

(MENU: Simulate > Run > Restart)

4 Run timerun.do again and note the difference in run time.

do timerun.do

Run time has been cut almost in half by inserting exits in the loops.

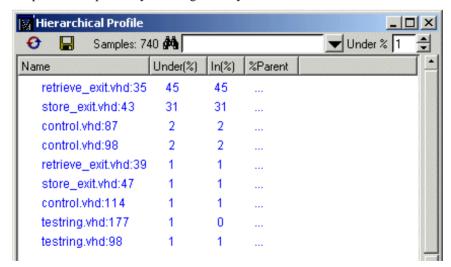

**5** Take another look at the Performance Analyzer data.

view\_profile

(MENU: Tools > Profile > View hierarchical profile)

A lot of time is still being spent in the loops. To further reduce simulation time, these loops can be replaced by indexing an array.

**6** Remove the loops and add an array, or compile the following files which already contain the modifications.

vcom retrieve\_array.vhd store\_array.vhd

(MENU: Compile > Compile)

7 Compile the top-level blocks and configuration files again.

vcom ringrtl.vhd testring.vhd config\_rtl.vhd

(MENU: Compile > Compile)

**8** Restart the simulation with the modified files.

restart -f

(MENU: Simulate > Run > Restart)

**9** Run *timerun.do* again and note the difference in simulation run time. Your time may differ from that shown here, but the new run should be very fast – roughly ten times faster than the original simulation time.

do timerun.do

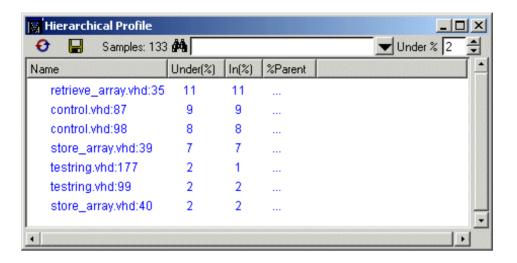

10 Look again at the Hierarchical Profile and you will see more lines showing.

view\_profile

(MENU: Tools > Profile > View hierarchical profile)

Note: Your results may look slightly different as a result of the computer you're using and different system calls that occur during the simulation.

**11** Set the Under% filter to "2" and click the Update icon. This will filter out all usage values below 2%.

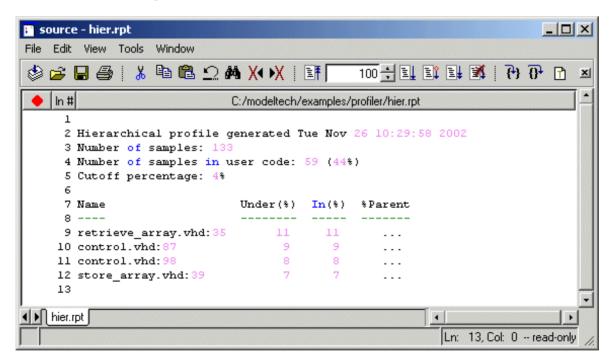

**12** Use the report command to output a file with the profile data.

```

profile report -hierarchical -file hier.rpt -cutoff 4

```

This command outputs a hierarchical profile of performance data with the file name *hier.rpt*.

**13** Quit the simulation.

quit -f

# **Lesson 9 - Simulating with Code Coverage**

### The goals for this lesson are:

- Create a new project for code coverage

- Compile the project

- Load and run the project with code coverage

- View code coverage statistics

- Create code coverage reports

- Exclude lines and files from coverage statistics

- Merge coverage results from two simulations

ModelSim Code Coverage allows you to identify which statements and branches in your code are being executed by the testbench. Coverage data is collected on an instance by instance basis, with statement and branch executions counted for each instance. Multiple statements on a line are counted individually. Reports show the line number and character number of the last character in the statement. Conditional "if" and "case" statements are collected as branch statistics – each "hit" of a true or false condition in an if statement is counted.

Code Coverage allows you to use pragmas to turn code coverage off and on. You can merge the results of multiple tests, making it possible to use multiple test benches or multiple stimulus files. And Code Coverage is non-intrusive (instrumented code is *not* required) and only minimally impacts simulation performance (typically 5-10%).

# Create a new project for code coverage

- 1 Create a new working directory, make it the current directory, and copy the files from <install directory>\modeltech\examples\coverage into it.

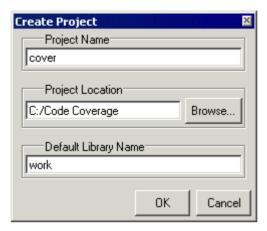

- 2 Start ModelSim and select File > New > Project to open the Create Project dialog.

- **3** Type "cover" in the Project Name field.

- **4** Browse to the location of your current working directory.

- **5** The Default Library Name should be "work."

- 6 Select OK to create the new project, *cover.mpf*. This will open the **Add items to the Project** dialog.

- 7 Select **Add Existing File** and add all files from the new working directory you created in step 1 above. See "Creating a project" (T-12) in *Lesson 1* if you need a reminder on how to do this operation.

# Compile the project

1 Compile the files using the **vlog** and **vcom** commands.

vlog Micro.v Modetwo.v Pre.v vcom Tx.vhd Buffers.vhd Delta.vhd Fifo.vhd Fs\_add.vhd Post.vhd testdel.vhd Arb.vhd

(Menu: Compile > Compile All)

Note: The "No default binding" warning messages that diplay in the Transcript window are related to the compile order of the files. These message are expected and do not affect the simulation.

# Load and run the project with code coverage

1 Use the **vsim -coverage** command to load the design with code coverage invoked.

vsim -coverage work.test\_delta

(Menu: Simulate > Simulate)

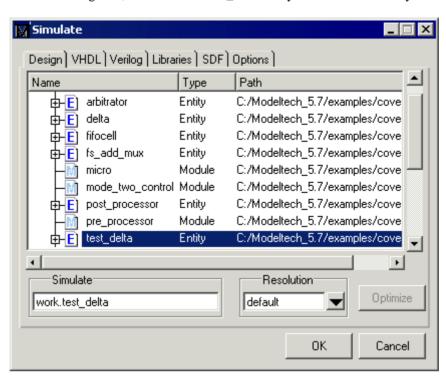

To load the design using the graphic interface (instead of using **vsim -coverage** at the command line) select **Simulate > Simulate** from the Main menu, or click the Simulate icon. Either action will open the Simulate dialog shown below.

Select the Design tab, then select the *test\_delta* entity from the work library.

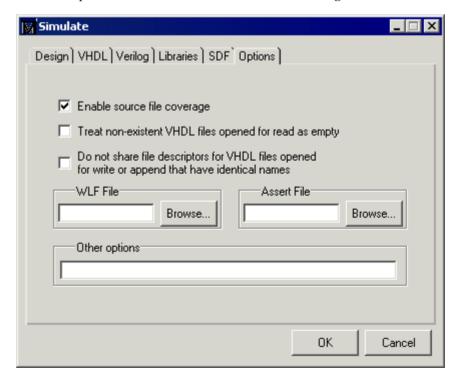

Select the Options tab and check Enable source file coverage.

Click OK to load the design with code coverage invoked.

**2** Run the simulator for 1 millisecond.

run 1 ms

(You'll see some initialization warnings in the Main window transcript due to unknown states of some instances. These will not affect the operation of the design created for this tutorial. For details on how to disable initialization warnings, see the **when** command in the Command Reference.)

# View code coverage statistics

Code coverage statistics can be viewed in both the Main and Source windows.

#### **Main window statistics**

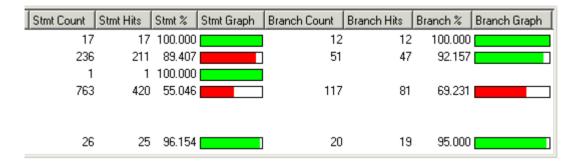

When a design is loaded with code coverage invoked, the columns shown below are added to the Files and sim tabs of the Main window Workspace. The performance of "if" and "case" conditional statements are collected as branch statistics.

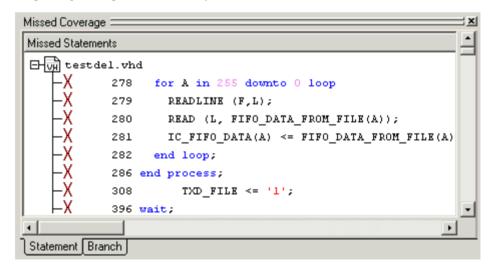

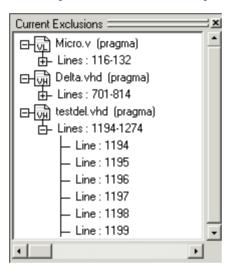

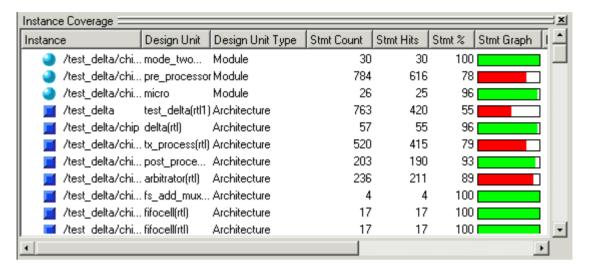

In addition, code coverage statistics are displayed in the following three panes of the Main window: Missed Coverage, Current Exclusions, and Instance Coverage. The Missed Coverage pane lists statements and branches that have not been executed (zero hits) according to their line numbers. The Current Exclusions pane lists user and pragma exclusions from code coverage statistics according to line number. The Instance Coverage pane lists statement and branch coverage statistics for each instance in a non-hierarchical display.

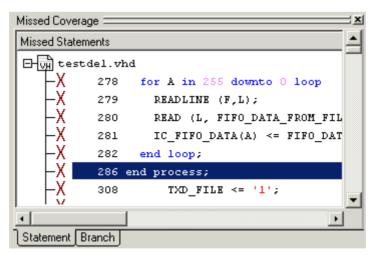

1 Select the *testdel.vhd* file in the Files tab of the Main window Workspace. This will place the missed coverage statistics for testdel.vhd in the Missed Coverage pane. Click the plus sign to expand the hierarchy as shown here.

The Missed Coverage pane includes coverage information for both missed statements and missed branches. Select the Branch tab to display missed branches.

- **2** Select any statement or branch in the Missed Coverage pane to display that item in the Source window.

- 3 Right-click any statement or branch in the Missed Coverage pane to open the Exclude Selection button, which allows you to exclude your selection from the code coverage statistics. If you choose to exclude a line, you will see that line displayed in the Current Exclusions pane.

- 4 The Current Exclusions pane displays all user and pragma exclusions for the design. Click the plus and minus boxes to expand and contract the displayed hierarchy.

Right-click any item in the Current Exclusions pane to open a context menu. With this menu you can cancel the exclusion of the selected (non-pragma) item, load or save an exclusion file, and hide or show pragma exclusions.

5 The Instance Coverage pane displays statement and branch coverage statistics for each instance in a flat, non-hierarchical view. Select any instance in the Instance Coverage pane to see its source code displayed in the Source window.

**6** Right-click any item in the Instance Coverage pane to open a context menu. This menu allows you to create coverage reports, set a display filter, or clear code coverage data for every item in the design.

#### Source window statistics

Code coverage statistics are displayed in the Source window when coverage is invoked.

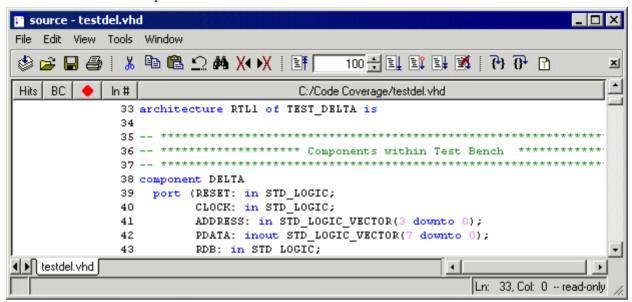

You can view the source code for specific modules or entities by double-clicking an item in the Files or sim tab of the Main window Workspace, or by selecting any item in the Missed Coverage or Instance Coverage panes.

1 In the Files tab of the Main window Workspace, double-click the *testdel.vhd* file to open it in the Source window.

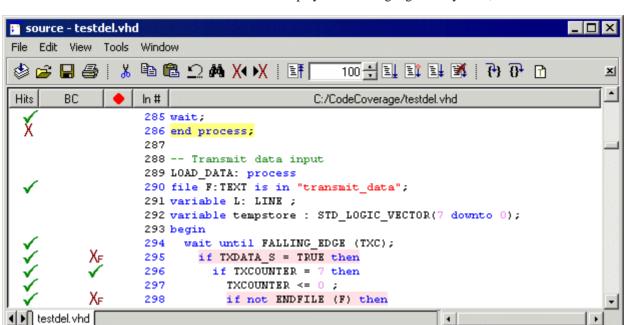

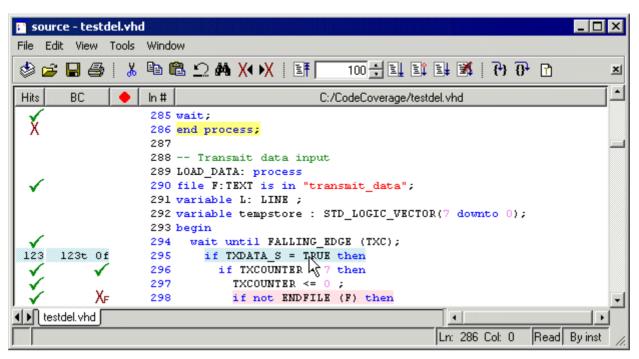

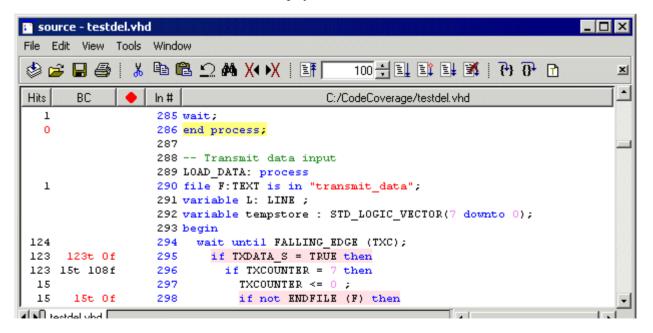

**2** To go directly to a line of code that contains a statement that has not executed, click the plus sign next to the *testdel.vhd* file name in the Missed Coverage pane (with the Statement tab selected) and select line 286.

The Source window now displays line 286 highlighted in yellow, as shown below.

A red X in the Hits column indicates that a statement in that line has not been executed (zero hits). A green E in the hits column indicates a line that has been excluded from code coverage statistics. A red  $X_T$  or  $X_F$  in the BC (Branch Coverage) column indicates that a true or false branch (respectively) of a conditional statement has not been executed. Lines that contain unexecuted statements and branches are highlighted in pink.

Ln: 286 Col: 0

By inst

**3** Hover the mouse cursor over the code for line 295 as we've done below. You will see the checkmark in the Hits column and the X<sub>F</sub> in the BC column change to numbers – indicating the number of times the statements and branches in that line were executed.

The BC column displays the number of hits of both true and false conditions. In this case the true branch was executed 375 times and the false branch was not executed.

4 Open the Source window's View menu and select Show coverage numbers. The Hits and BC columns will display execution counts instead of checkmarks and X's.

# Create code coverage reports

ModelSim allows you to create code coverage reports using the graphic interface or by entering commands at the command line.

#### Coverage reporting with the graphic interface

You use the Coverage Report dialogto create coverage reports via the graphic interface. This dialog can be opened with any of the following three methods: 1) select **Tools** > **Coverage** > **Reports** from the Main window menu; 2) right-click any item in the Workspace of the Main window and select **Coverage** > **Coverage Reports** from the context menu (and submenu); 3)right-click any item in the Instance Coverage pane and select **Coverage reports** from the context menu.

- 1 Select **Tools > Coverage > Reports** from the Main window menu.

- 2 Select **Report on all instances** and **No Filtering**. Leave the Other Options unselected.

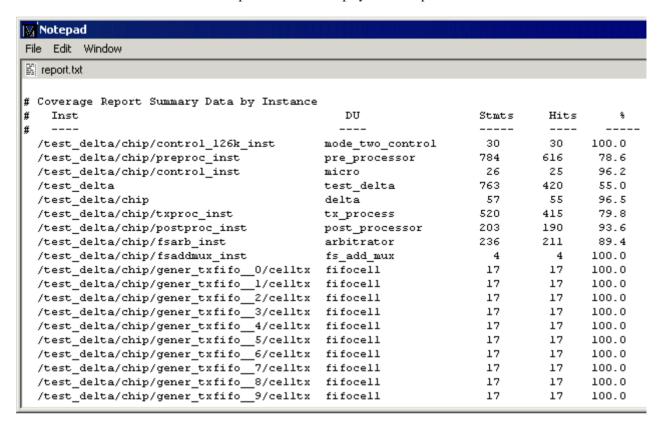

**3** Use the default report pathname, *report.txt*, or assign a new one; then click OK. This will create a report that will be displayed in Notepad as a text file.

- 4 Close Notepad.

- 5 Select **Tools** > **Coverage** > **Reports** again from the main menu.

- 6 Select Report on a specific instance.

- 7 In the Instance Name field enter "sim:/test\_delta" (without quotes) or browse to select it.

- 8 Select No Filtering and the Include Line Details option.

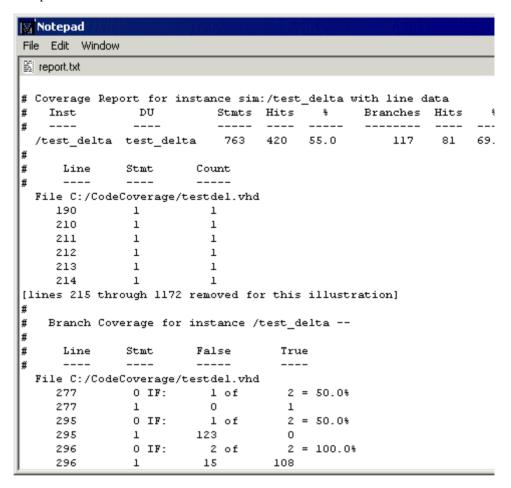

**9** Enter a new report pathname. ModelSim will create the report and display it in Notepad as shown below.

Experiment with the other code coverage reports and filters available with the Coverage Report dialog.

#### Coverage reporting at the command line

ModelSim gives you the ability to create reports from the command line using the **coverage report** command.

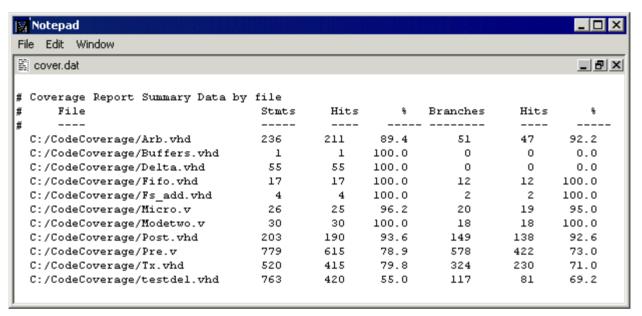

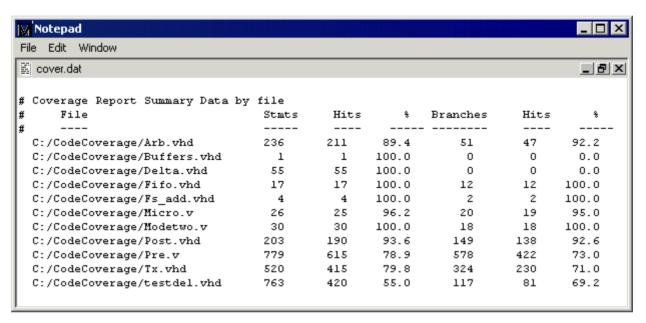

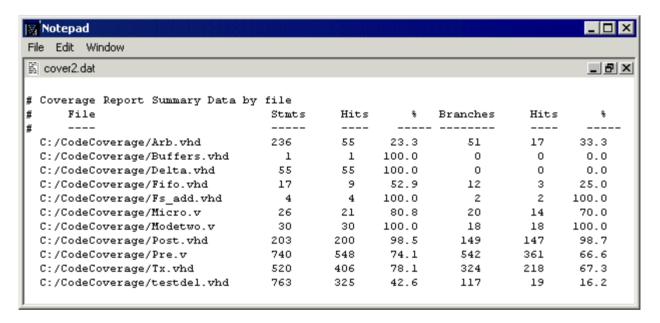

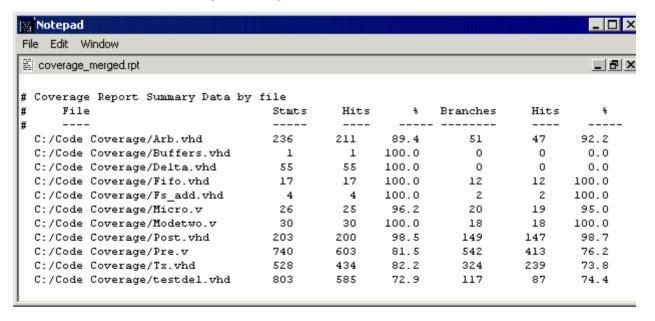

1 To save a summary of the code coverage statistics by source file, enter the following command at the command line:

coverage report -file cover.dat

**2** Open the file *cover.dat* to see how the data is stored. The **notepad** command works well for getting a quick view of text files.

notepad cover.dat

See the **coverage report** command in the *ModelSim Command Reference* for complete details on creating reports at the command line.

# Exclude lines and files from coverage statistics

ModelSim allows you to exclude lines and files from code coverage statistics using the graphic interface, the **coverage exclude** command, or by setting pragmas in the code.

#### Using the graphic interface

- 1 If it is not already selected, select the Files tab in the Main window workspace.

- 2 Right-click the *Modetwo.v* file and select Coverage > Exclude Selected File.

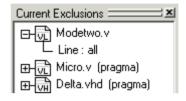

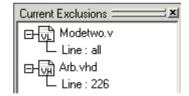

Modetwo.v will appear in the Current Exclusions pane.

You can also exclude lines from coverage statistics using the Missed Coverage pane.

- 3 Select the *Arb.vhd* file from the Files tab of the Main window Workspace. This will make *Arb.vhd* appear in the Missed Coverage pane.

- **4** From the Statement tab of the Missed Coverage pane click on the plus sign associated with *Arb.vhd* to show all statements that have not executed.

- **5** Right-click line 226 to select it and bring up the **Exclude Selection** button.

- 6 Click the Exclude Selection button. The Arb.vhd file will appear in the Current Exclusions pane as shown here.

To cancel an exclusion from the graphic interface, right click any item or items (except pragma exclusions) in

the Current Exclusions pane and select **Cancel Selected Exclusions** from the context menu.

#### Using the coverage exclude command

The **coverage exclude** command loads an exclusion filter file. Exclusion filter files specify files and line numbers that you wish to exclude from Code Coverage statistics. The proper syntax for using the **coverage exclude** command is:

```

coverage exclude <filename>

```

where <filename> is the name of the exclusion filter you wish to load. Excluded files will appear in the Current Exclusions pane.

#### Setting pragmas in the source code

ModelSim supports the use of source code pragmas to turn coverage off and on. In Verilog the pragmas are:

```

// coverage off

// coverage on

```

In VHDL, the pragmas are:

```

-- coverage off

-- coverage on

```

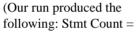

For this example we'll arbitrarily exclude lines 709 through 791 from the Pre.v Verilog file. Before we exclude these lines, make note of the statement and branch counts, hits and percent coverage for the Pre.v file in the Files tab of the Main window Workspace. (Our run produced the following: Stmt Count = 779, Stmt Hits = 615, Stmt % = 78.947, Branch Count = 578, Branch Hits = 422, Branch % = 73.010)

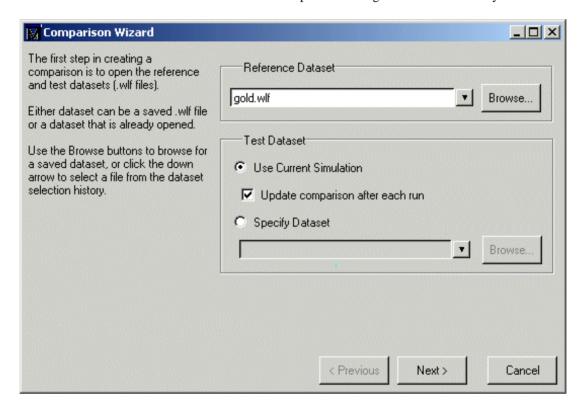

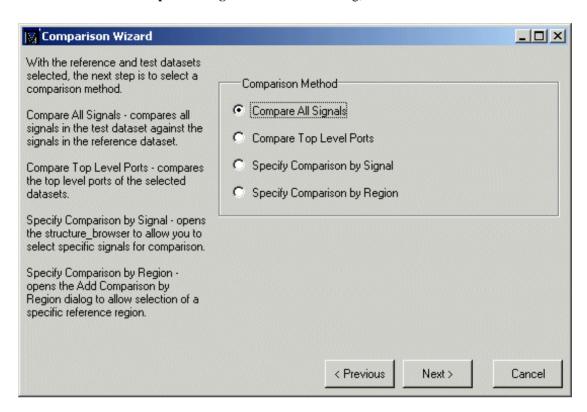

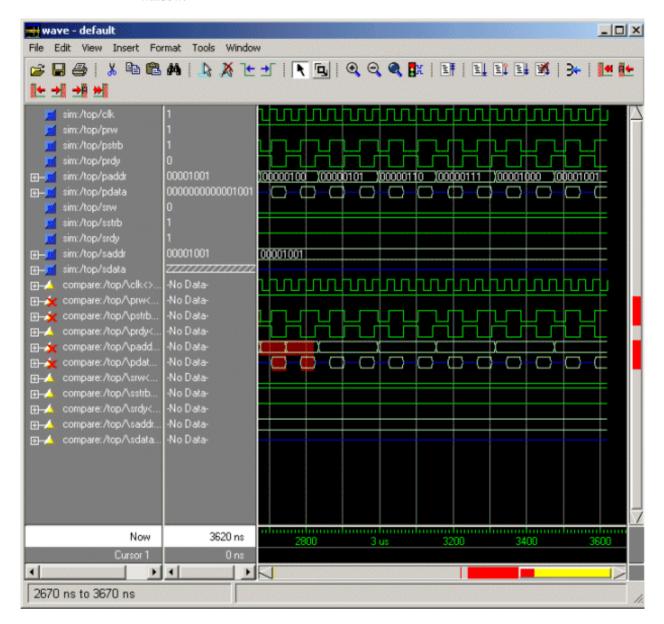

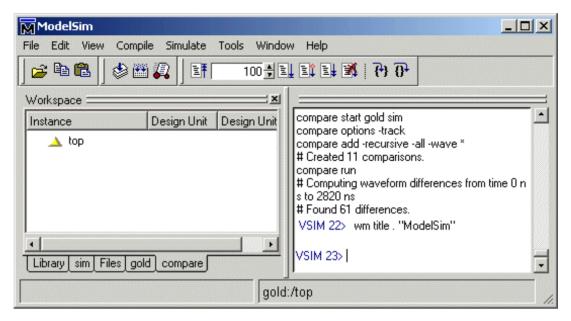

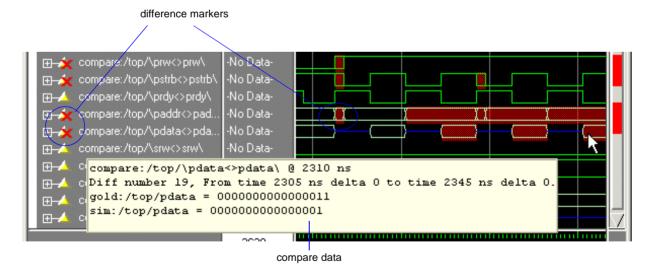

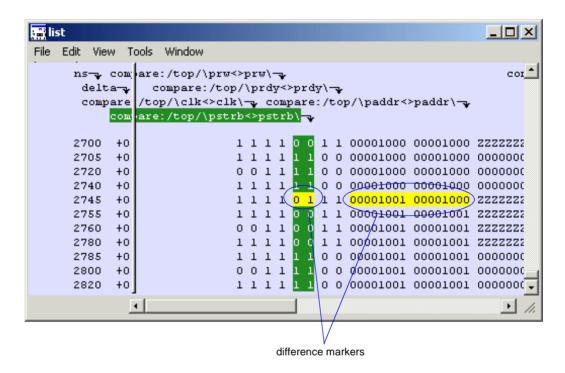

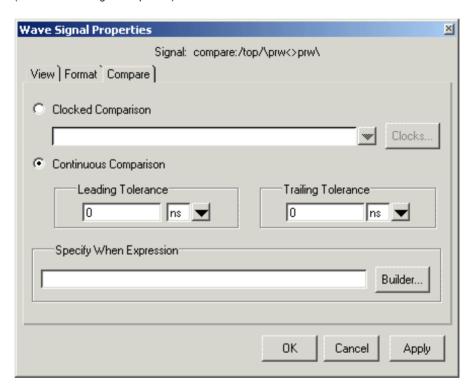

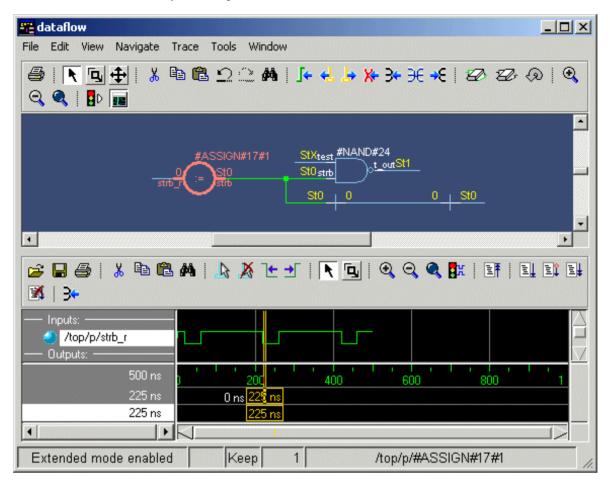

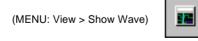

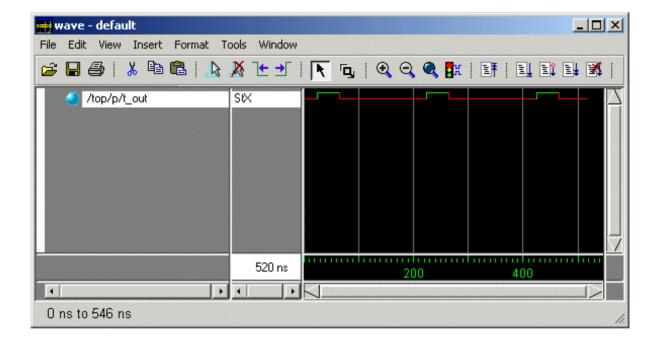

- 1 Double-click the *Pre.v* file in the Main window workspace to open it in the Source window.