# **RASSP Design For Testability (DFT) Appnote**

## Abstract

The RASSP program has significantly benefitted with the development of the DFT Methodology and its application to the Benchmark efforts. RASSP Design For Testability ensures that hardware and software for a signal processing system is testable during all RASSP life cycle phases and that the system complies with all customer supplied requirements. DFT also generates significant economic benefits which reduce the overall life cycle cost of a product. Based upon a singular test philosophy of the DFT methodology the life cycle testability support concept .

## Purpose

This note describes the role of DFT in the RASSP methodology and summarizes the life cycle singular test philosophy, procedures, and tools developed during the RASSP program. Technological and economic benefits produced by application of DFT to signal processing systems is also described and illustrated by examination of two benchmark projects.

## Roadmap

1.0 Executive Summary

- 1.1 The Design For Test (DFT) Methodology Complete Life Cycle Testability Support

- 1.2 The DFT Application Process Tools and Design Element Reuse

- 1.3 Summary of DFT Contribution to RASSP

- 2.0 Introduction

- 3.0 Technology Description

- 4.0 Application Example

- 4.1 Problem Definition and Approach to Solution

- 4.2 Stepwise Application of Methodology

- o 4.2.1 Dependency Modeling to Support Architecture Selection

- o 4.2.2 Collection and Specification of Requirements

- 4.2.3 Requirements Consolidation and Test Strategy Selection Singular Test Philosophy Development

4.2.3.1 Steps 1 through 9

- o 4.2.4 Generation of TSDs and Test Architecture

- □ 4.2.4.1 TSD Transfer Function Values

- □ 4.2.4.2 TSD Test/Time Cost Attribute Values

- □ 4.2.4.3 TSD Implementation

- o 4.2.5 Test Procedure Development

- 4.2.6 Board Level Application of DFT Design Tools

- □ 4.2.6.1 VHDL Component Modeling

- □ 4.2.6.2 Testability Analysis and Interconnection Testing

- □ 4.2.6.3 FPGA-Based Board Level ABIST

- 4.3 Technical Summary of Application Example

- 4.3.1 Tool Application Summary

- o 4.3.2 Reuse Élement Listing

- o 4.3.3 Lessons Learned

- 4.4 DFT Economic Analysis

- 4.5 Application Example Conclusions/Summary

- 5.0 References

Approved for Public Release; Distribution Unlimited Dennis Basara

Next: 2 Introduction Up: Appnotes Index Previous: Appnote DFT Index

# **RASSP Design For Testability Application Note**

## **1.0 Executive Summary**

# **1.1** The Design For Test (DFT) Methodology - Complete Life Cycle Testability Support

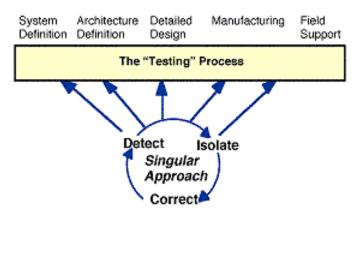

The RASSP program has significantly benefitted with the development of the DFT Methodology and its application to the Benchmark efforts. RASSP Design For Testability ensures that hardware and software for a signal processing system is testable during all RASSP life cycle phases and that the system complies with all customer supplied requirements. DFT also generates significant economic benefits which reduce the overall life cycle cost of a produject. Based upon a **singular test philosophy** of the DFT methodology tThe life cycle testability support concept based upon a singular test philosophy of the DFT methodology is illustrated below in Figure 1-1 and includes along with a listing of technical objectives and benefits of the DFT methodology.

# RASSP DFT Methodology

## TECHNICAL OBJECTIVES

Develop singular test philosophy across all life cycle phases supported by a methodology using commercial tools

- Introduce DFT as early as possible to reduce cost/time for test at all life cycle phases

- Develop ABIST and BSCAN tools (LV Software) that can support board design

### BENEFITS

Consolidated requirements set maximizes reuse to minimize test development costs

- Offer potential cost reduction during each life cycle phase (design, manufacturing, field support)

- · Reduce project life cycle test cost by 2.3X

- · Reduce cost of test in manufacturing by 2.7X

- · Reduce product life cycle cost up to 20%

- Standardized reusable test strategies and testability building blocks enhance reuse

Figure 1 - 1: RASSP Uses a Common DFT Methodology Across All Project Phases.

#### **1.2 The DFT Application Process - Tools and Design Element Reuse**

Application of tThe DFT methodology is initiated by generating a set of **consolidated test requirements** fromby a team of experts with design, manufacturing, and field deployment experience. These requirements are processed to yield **Test Strategy Diagrams** (TSDs) that support and a singular test philosophy which applies (to the extent possible) a

common test strategy to all life RASSP life cycle project phases. The TSD is an EXCEL spreadsheet based utility that manages (distributes) requirement allocation to all packaging levels and monitors multilevel conformance to these distributed requirements. In parallel with the TSD developmentSimultaneously, a complete supporting test architecture (TA) shown in Figure 1-2 is developed which specifies:

- 1. testbenches for design simulation,

- 2. details of board level DFT and BIST features, and

- 3. detailed specification of test equipment and test program sets (TPSs) is developed. This is followed by the developmentFinally of, detailed test plans and the procedures which implement these plans are developed.

DFT insertion begins during system design. It, is developed during simulation., and isThen it is installed and then validated in a prototype. This leads tolt then supportings manufacturing test, and eventually becominges a major part of (or the sole source of) the field supportability for a delivered system.

#### **1.3 Summary of DFT Contribution to RASSP**

RASSP DFT has developed a methodology that provides for the insertion of to insert DFT enabling features into signal processing system designs and contributess significantly toward the RASSP 4X time and cost improvement goals. In addition to demonstrable testability improvements, DFT offers;

- 1. the potential for up to a 20% reduction in life cycle cost,

- 2. a pre-DFT to post-DFT test cost ratio of 2.3, and

- 3. a post-DFT to pre-DFT reduction factor for manufacturing test cost of 2.7X.

Next: 2 Introduction Up: Appnotes Index Previous: Appnote DFT Index

Approved for Public Release; Distribution Unlimited Dennis Basara

Next: 3 Technology Description Up: Appnotes Index Previous: 1 Executive Summary

# **RASSP Design For Testability Application Note**

## **2.0 Introduction**

This Application Note is intended for system engineers and design engineers developing signal processing systems. The system engineer is presented with a methodology for incorporating DFT into a project to ensure compliance to customer requirements across the complete RASSP project life cycle. The design engineer is shown how to develop a complete testing approach in a verified design which translates directly to a product.

The RASSP DFT insertion methodology is demonstrated by application to all phases of one of the RASSP Benchmark 3 benchmark projects (Benchmark 3). Using systems fabricated from today's high density packaging systems which compress functionality at the expense of accessibility, the BM3 application illustrates how DFT inserts **full life cycle** (i.e., system design to field deployment) testability. Also examined are tinto systems fabricated using current high density packaging systems which compress functionality at the expense of accessibility. The economic benefits of DFT are also examined across the project life cycle and potential for life cycle cost (LCC) reduction is examined.

The system engineer applies the DFT methodology to **develop unambiguous**, **quantifiableed requirements**. **and to Aassistance is also provided in the process of architecture trade off and selection**. Testability insertion begins as consolidated requirements are developed by an integrated expert team representing design, manufacturing and field engineering project phases. The collaborative approach ensures that no single project phase is emphasized at the cost of another and that the end system will be optimized for testability throughout its life cycle. CReceived customer requirements are examined to ensure that they are consistent, realizable and valid. **Test means** for requirements verification are examined and a **singular test philosophy (STP)** is developed. Tthat maximizes the effectiveness of the selected DFT approach over the product life cycle is maximized by by using tests common to all life cycle phases is developed.

The design engineer **verifies** the operation and effectiveness of selected DFT features along with the functional system simulation. Component selection accompanies simulation to ensure that test circuitry can be integrated into the system hardware and software. IEEE 1149.1- and BIST (Built In Self Test) - enabled components and a complementary physical test bus architecture are added to board layouts. Test vectors are generated to be applied to DFT elements added to a design. Board level BIST technology is added to extend test coverage. A full set of test procedures is developed to meet the needs of development, manufacturing and deployment testing of the hardware.

**RASSP DFT is supported with an extensive toolset** and reusable templates supporting DFT during all the RASSP life cycle phases. Consolidated requirements are template based to ensure completeness. Test Strategy Diagrams (TSDs) implemented as EXCEL spreadsheets derived from the consolidated requirements distribute the requirements to lower packaging levels and support enforcement of requirements. A complete test architecture developed in parallel with the TSDs supplies a full set of test plans and procedures which measure compliance to requirements. A complete set of VHDL-based simulation and test vector generation tools supports development of JTAG--based tests and installation of board level BIST which maximizes hardware testability during manufacturing and field deployment. Any required supplementary ATE (Automatic Test Equipment) testing is also supported by definition of critical test points not covered by JTAG or BIST testing.

Next: 3 Technology Description Up: Appnotes Index Previous: 1 Executive Summary

Page Status: in-review, January 1998 Dennis Basara

Next: 4 Application Example Up: Appnotes Index Previous: 2 Introduction

## **RASSP Design For Testability Application Note**

## 3.0 Technology Description

RASSP Design For Test technology has inserted testability into all phases of the RASSP methodology (**RASSP Methodology Version 2.0**) - from system design to field support. This insertion has been accomplished using a combination of existing and modified commercial simulation, CAD, and specialty DFT tools. along with Sseveral of the DFT specialty tools were developed during the RASSP program.

During early project phases, DFT influences the functional analysis and alternative architecture alternative evaluation and functional analysis viathrough the enabling technology of **functional dependency modeling** (DM) which examines testability of a system at the functional block diagram level. DM technology defines faults and tests for each system function and permits a parametric analysis of the consequences of limited measurement capability of each of the system functions. The designer uses "What if" analysis to rate the testability performance of alternative architectures and different proposed physical implementations of system functions.

A technology **developed** during the RASSP program is **template based requirements analysis**. Templates ensure uniform, unambiguous expression of requirements by an integrated product development team (IPDT) with expertise in the areas of design, manufacturing, and field support. **Consolidated test requirements** used throughout a project life cycle contain both customer and derived requirements added to ensure quality and producibility in the end product. The system designer is forced to examine each requirement from the viewpoint of eventual quantitative measurement to establish that each requirement is consistent, realizable and valid.

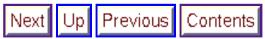

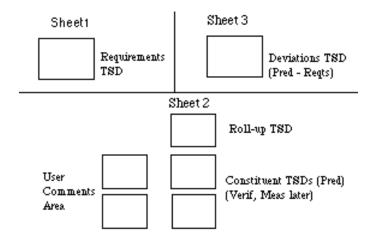

After requirements are defined, a **singular test philosophy (STP)** applicable to all life cycle phases is designed and expressed in a series of **test strategy diagrams (TSDs)**. As **can be seen in Figure 3-1, the TSDs** which allocate detection, isolation, and correction requirements across RASSP methodology phases and packaging levels for specific fault classes such as shorts, opens, and single stuck-at faults. TSDs are linked across RASSP phases and **upward and downward** in the packaging level dimension to implement both requirements distribution and compliance monitoring. Designers at any level interact with the appropriate TSD to confirm or deny the ability of a specific system element (e.g., board) to satisfy its allocated requirements. Contents of a typical TSD are shown below. TSDs can contain prediction, verification, or measured values. One TSD is used for each **fault class** such as **opens, shorts, and stuck-at faults**. Quantitative detection, isolation, and correction values are allocated across a series of test means and the total coverages for the fault class being controlled are calculated and displayed. Measurement and verification TSDs for a specific fault class are compared to the related prediction TSD to monitor requirements compliance. As described in the Application Example below, the TSD is implemented as a multisheet Microsoft EXCEL workbook. This format supports reuse by simple modification of TSDs developed on earlier projects to current projects.

# Anatomy of a Test Strategy Diagram

Faults are resolved by applying allocated test means to the processes of detection, isolation and correction. Each test means operates on a specific fault class to reduce the number of undetected, unisolated, and uncorrected faults. For each "box" shown, a fault population enters at the top or from the left. Successfully processed faults exit at the bottom and proceed to the next stage of the detection, isolation, correction cycle. Unsuccessfully handled faults exit to the right to be processed at the same stage.

Figure 3 - 1: Form and Contents of a Test Strategy Diagram.

As shown in Figure 3-1 and discussed in the Executive Summary, definition of the **test strategy** is accompanied by the following items:

- 1. definition of a supporting test architecture, including a testbench architecture to support design phase testing,

- 2. a testability architecture to define DFT/BIST features, and

- 3. a tester architecture to definedefine the physical implementation of the test strategy.

The test strategy and architecture result in **test plans** from which a set of **test procedures** areis developed. RASSP developed the framework to formalize the means needed to implement this test strategy.

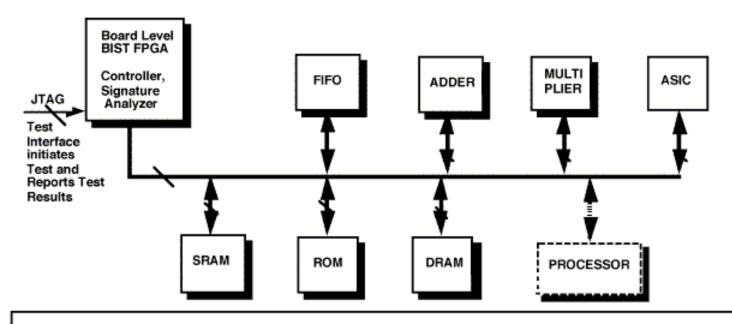

During design, DFT features such as **JTAG strings** and **FPGA-based board level BIST** are simulated on a VHDL testbench and their effectiveness is evaluated. Specialty tools designed to create and manage these features supply VHDL code used in the simulations and the test vectors required for testing during design and after when the design has been reduced to hardware. A technology driver in **testability analysis** and **test feature installation** for RASSP DFT was a technology driver in testability analysis and test feature installation and resulted in contributing refinements to commercial test tools (VICTORY, Parallel Port Tester) and development of several new BIST insertion tools (LogicVision). Simulation efforts result in verification of the proposed test approach and generatetest program sets (TPS) which will be used on the actual hardware. Satisfaction of **prediction** TSD-assigned hardware requirements to system components is verified and the path to actual performance **measurement** in hardware is established via reuse of the simulation TPS. In addition to Reuse enhancingenhance thes likelihood of first pass success for hardware test, and, in addition, reuse results in significant hardware-based test development time and cost economies.

Once simulation is completed, hardware prototypes are produced and physical testing begins. U using Test Pprocedures defined in the test architecture definition phase and now verified by the simulation exercises, physical testing is performed. Actual measurements during manufacturing and acceptance testing substantiate the satisfaction of all requirements, and the system is ready for field deployment where it is subject to the pre-established maintenance philosophy defined in the field phase measurement TSDs.

Next: 5 References Up: Appnotes Index Previous: 3 Technology Description

# **RASSP Design For Testability Application Note**

## 4.0 Technology Description

#### 4.1 Problem Definition and Approach to Solution

The major demonstrabledemonstration target for application of RASSP DFT methodology to a signal processor system was the **AN/UYS-2A functional element** (**FE**) as defined in the Benchmark 3 (BM3) project. The FE consisteds of one controller (called FPCTL) and two bus-oriented processor PC boards (called FPCAP) of moderate complexity. Components primarily included processors, memory devices, and FPGAs. Under the RASSP program, several BM3 FEs were fabricated for delivery and insertion into active AN/UYS-2-A systems for testing in accordanceing witho a short schedule. For this reason, DFT was applied in a non-interfering "shadow" mode in order to examine the addition of DFT to the FEs of BM3 without the risk of imposing new technology into thea time-critical development path. The full suite of DFT techniques was applied to the FE boards, mainly to the controller (FPCTL), as the hardware and supporting software were developed. The benefits of DFT inclusion were demonstrated during simulation exercises. Application of DFT technology in the serial manner described in the **RASSP Design For Testability (DFT) Methodology Version 1.0** document resulted in a sound test strategy which provides could enhancements fore future versions of the FE hardware. DFT application to the BM3 FE **also advanced the state-of-the-art of PC board test coverage** to memories and other components with regular structures which had not previously been testable by on-board means.

#### 4.2 Stepwise Application of Methodology

Application of DFT methodology can be described in a sequence of six basic steps deployed throughout the project life cycle.

#### 4.2.1. Dependency Modeling to Support Architecture Selection

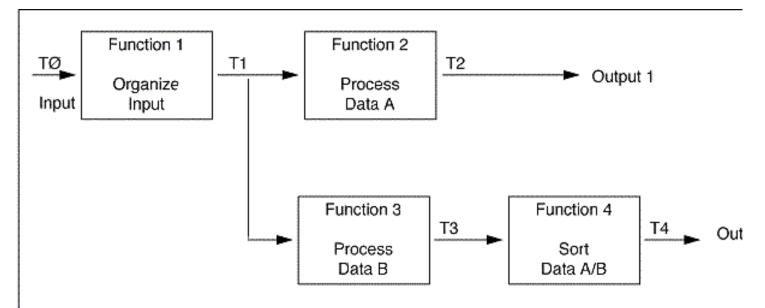

Functional Dependency Modeling (DM) is a tool that allows DFT analysis to begin during the earliest stages of a project. DM consists of developing a model of the dependency relationships among system functions to allow effects of failure of any function to be propagated to all succeeding functions. Failure modes for each function are defined and the DM tool identifies consequences of designer-initiated assertions of failures on succeeding functions and on the entire system. DM tools implement a form of propositional logic to model tests, failure modes and the interdependencies of these entities. For RASSP, it is first applied during concept definition and its use continues through architecture investigation and selection phases. For BM3, DM was used to locate ambiguous (indistinguishable) faults on both the FPCAP and FPCTL boards and to identify consequences of potentially inaccessible circuit nodes. In so doing, DM was used to support **selection of a preferred architecture** from the testability viewpoint. Two tools, WSTA by Naval Undersea Warfare Center (NUWC) and STAT by Detex Systems Inc., were used for parametric "what if" analyses of functional block diagrams (FBD) ofor both types of boards used in the BM3 FE. Functional block diagrams are pictorial representations of a system's functional elements and their interrelationships. They are constructed by system engineering during concept development. FBDs indicate how each system function depends upon the others of the complete set. Certain functions, for example, will execute successfully if related previous functions execute properly. Conversely, failurs introduced early into a functional chain typically result in observations of failures in execution of one or more subsequent functions.

The most significant testability information supplied by DM was :

- a recommended binary test strategy tree an **ordered sequence of tests alternatives** selected from a binary tree structure based upon a PASS/FAIL result for each test as it is executed

- recommendations for an optimized BIT (Built In Test) a series of tests which leads to the **quickest verification of a working system** this test series follows the PASS route from application of the first test through to the establishment of a **no-fault** condition

- identification of **test ambiguity groups** listings of components (and their **aspects**, or failure modes) which could be responsible for indication of failure by a given test. An ambiguity group larger than unity implies that a failure cannot be isolated to a single component. Ambiguity group data can signal existence of potential design problems early in the system design phases.

- recommendations for **addition of tests** specified as **excluded** by the analyst during "what if" tradeoff analysis. Testpoint access can be controlled during DM analysis to identify a test sequence which supports a minimal

cost/time strategy. When excess restriction of test point access is imposed, testability becomes impaired. Test addition recommendations are indicators of this condition.

Dependency modeling is particularly useful in gaining insight into system testability very early in the design process, even **at the concept phase, as soon as the functionality of the system has been defined.** Figure 4-1 illustrates the concept of a Functional Block Diagram. and ill also can continue to make significant contributions to the system development through architecture selection. A special feature of DM is that the model remains completely adaptable to the level of system information available at the time of the testability examination. More than one modeling exercise is likely as the system design continues to evolve.

- TØ, T1, T2... represent tests defined to validate system at a particular point of application

- Success/failure of test T2 at Output 1 depends upon success/failure of tests TØ and T1

- Success/failure of test T4 at Output 2 depends upon success/failure of tests TØ, T1, T2 and T3

Figure 4 - 1: Example of Functional Dependency Model.

During concept development, time- and cost -independent dependency modeling can provide a definition of ambiguity groups resulting from imposition of test point restrictions and can give a very early indication of testability problems. As the system becomes better defined, test time and test cost can be factored into a dependency model if the designer can supply estimated or actual values for component mean time between failure (MTBF) and mean time to repair (MTTR). It is also possible for the user to prioritize known component function criticality. The DM recommended test strategy will be biased by the relative values of these three factors.

For candidate architectures, during architecture tradeoffs and selection, quantitative trade-offs based on:

- 1. the number and size of ambiguity groups;,

- 2. extent of BIT;,

- 3. test strategy complexity; and

- 4. cost and repair time can be used to quantify criteria for candidate architectures being compared.

Dependency models are useful in identifying opportunities or requirements for adding specific testability features. Models can be exercised by denying access to selected test points associated with functions in the model. Access restriction corresponds to simulating a system with real physical accessibility limitations. For BM3, the Myrinet interfaces and associated RAM were, in fact, practically restricted because of bus speed and special low (1.6V) voltage requirements. No standard test equipment would likely be able to evaluate the status of these components at the board level. Dependency analyses quickly identified the ambiguity groups created by the restrictions and made this information available to the designers. The tool thus provided the designer an **early alert to testability problems**. DM also revealed that isolated FPCTL or FPCAP boards presented challenges to testability individually but when connected together, the combination

possessed alternative access paths which could evaluate operation of difficult to test components. DM can thus detect a potential problem and may also suggest possible solutions.

#### 4.2.2. Collection and Specification of Requirements

A multi-step procedure was developed to achieve a **consolidated requirements set** having significant commonality across design, manufacturing, and field deployment project phases. First, candidate requirements were selected by a **team** consisting of engineers and test support personnel with design, manufacturing, and field test expertise. Each individual represented his/her own area to ensure that **explicit customer requirements** would be met in each of the life cycle phases and to ensure that any **derived requirements** (not explicitly stated by the customer), needed to build quality and, reliable equipment would be added to the formal requirements list. Requirement **templates** designed to unambiguously quantify requirements and the means of their measurements were used to ensure sufficiency and consistency of representation of the requirement information. These populated templates were the primary output from the requirements generation process. The content of a requirements template is shown in Figure. 4-2.

# **Test Requirement Template**

| a. Test Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | e. Fault Model Assumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Design (e.g., simulation, prototype debug qualification test,<br/>etc.)</li> <li>Production (e.g., go/no test, diagnostic test, repair</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>The definition of a "fault." For example, single stuck<br/>fault, multiple stuck-at fault, delay fault intermittent<br/>transient fault, etc.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| verification, etc.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | f. Quantitative Definition of Metric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul> <li>Field (e.g., operational, organizational, intermediate, depot)</li> <li><b>b. Test Means</b> <ul> <li>BIST</li> <li>Test Equipment</li> <li>Manual procedures</li> <li>Mix of above</li> </ul> </li> <li><b>c. Test Mode</b> <ul> <li>Power-on test</li> <li>On-line concurrent (including interfering vs. non-interfering</li> <li>On-line non-concurrent (including periodic vs. event-driven, operator invoked or software invoked)</li> <li>Off-line</li> </ul> </li> <li><b>d. Degree of Allowable External Support</b> <ul> <li>Operator may be "in the loop" to help achieve requirement</li> <li>Troubleshooter may be "in the loop" to help achieve requirement</li> <li>Job performance aid may be used to help achieve</li> </ul> </li> </ul> | <ul> <li>An equation defining the metric. For example, fault detection coverage might be defined as the total nu of faults detected automatically by BIST, divided by number of possible faults, with "fault" defined by the model above.</li> <li><b>9. Prediction and Validation Weighing Factors</b> <ul> <li>The factors used to allocate the requirements and I to calculate system values from lower level values. example, failure rate, usage rate, mission criticality</li> <li><b>h. Quantitative Requirement</b></li> <li>The actual quantitative requirement, calculated by t "quantitative definition" above. For example "98%."</li> <li><b>i. Allowable Requirement Compliance Tracking Methodologies</b></li> <li>The means that may be used to track compliance to requirement throughout the life cycle of the system. example, topological dependency models at the prediction stage, fault simulation at the validation st</li> </ul> </li> </ul> |

| requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | and instrumentation or automatic fault-history loggi<br>the measurement stage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

4 - 2: Template Used For Quantitative Unambiguous Requirement Specification.

Collected requirements weare grouped into two classes :

- 1. conformance requirements, measured with a go/no-go test, typical of an acceptance test, and

- 2. **TSD-controlled** requirements, to be distributed hierarchically through all RASSP phases and to all packaging levels via a hierarchy of test strategy diagrams described below in step 4.0 of the Methodology application.

# **4.2.3. Requirements Consolidation and Test Strategy Selection - Singular Test Philosophy Development**

Requirements consolidation consists of collecting all customer defined requirements and integrating them with a supplementary set of RASSP process-related and fundamental fabrication quality requirements. This combination ensures that all customer needs will beare satisfied, that advantages associated with use of the RASSP DFT methodology will be realized and that quality equipment will be manufactured and delivered to the field. The steps summarized in Table 4-1 were followed to generate the set of consolidated requirements.

#### Table 4 - 1: Summary Procedure For Requirements Consolidation

| Create a set of requirement templates for the 3 project phases: design, manufacturing, and field support                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I                                                                                                                                                                                                                                                                                                                                                       |

| Check the inter-phase inherited anomalies for consistency and completeness: design flaws escaping to manufacturing , design flaws escaping to field, and manufacturing faults escaping to field                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                         |

| Within each project phase, look for opportunities to merge the identified flaws/faults within the specific phases.<br>Consider <b>test means</b> and <b>available support</b> as first level bases of comparison. Document differences, if<br>any, in <b>quantitative requirements</b> for requirements which are merged.                               |

|                                                                                                                                                                                                                                                                                                                                                         |

| Scan through all test phases for common test means at <b>detection</b> and <b>isolation</b> coverage levels. Do <b>not</b> consider the inherited faults in this comparison. Formulate a preliminary core Singular Test Philosophy (STP). Also do not consider correction coverage since, in most cases, the test means will be manual procedures only. |

|                                                                                                                                                                                                                                                                                                                                                         |

| Consolidate the merged requirements formed in Step 3 across the 3 test phases with the intent of applying the preliminary STP to <b>all</b> phases, if possible. Several possibilities exist:                                                                                                                                                           |

| • the STP applies to the 3 sets of preliminary merged requirements                                                                                                                                                                                                                                                                                      |

| • the STP can be modified by addition, deletion, or reordering during negotiations among representatives of design, manufacturing, and field                                                                                                                                                                                                            |

| individual templates can be modified to force conformance to the STP                                                                                                                                                                                                                                                                                    |

| individual templates can be tagged as not compatible with the preliminary STP                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                         |

| Examine applicability of the STP to the inherited requirements. Negotiate an agreement on the STP by any of the means identified in Step 5.                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                         |

| Perform final consolidation by negotiation among the 3 phases:                                                                                                                                                                                                                                                                                          |

| • choose a final STP                                                                                                                                                                                                                                                                                                                                    |

| add phase-specific supplemental items to the STP as required                                                                                                                                                                                                                                                                                            |

| modify individual templates to conform to the STP as required                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                         |

| 8. | Document the STP along with any exceptions and attach the documentation to the Consolidated Requirements Document. |

|----|--------------------------------------------------------------------------------------------------------------------|

|    |                                                                                                                    |

| 9. | Sign off the Consolidated Requirements Document.                                                                   |

A test strategy is a specification for an ordered application of a series of test means which will lead to defined levels of coverage for detection, isolation, and correction of specified fault classes. Coverage specifications are quantified and measurement techniques are specified in detail in the requirements templates. RASSP DFT seeks a test strategy called a **singular test philosophy (STP)** which is a strategy that can be applied during design, manufacturing, and field deployment. It is a desired goal because it allows reuse of test stimuli developed during simulation in manufacturing and in the field. The need for specialty tests is minimized and significant costs associated with development of phase specific test program sets (TPS) are eliminated or greatly reduced.

For BM3, common sets of test means to cover the phase-specific faults for each project phase were relatively easy to extract. A pattern of BIST followed by Boundary Scan test followed by less automated testing means was developed in each case. Negotiation sessions among the phase experts then examined the test means series extracted from the design, manufacturing and field environments with the intent of discovering possible application of a test means series **across** all phases. Examination again showed that a preferred arrangement existed - BIST, Boundary Scan (BS) Automated Test Equipment (ATE), non-BS ATE, and manual test. In some cases this basic series needed to be supplemented by means such as inspection or simulation. As will be discussed in more detail in the steps presented in the following example, an STP did exist for BM3.

An example of using the individual steps identified in Table 1 and applied to BM3 will now be discussed. The cost-benefit analysis of applying these steps to a project can be found later in this Application Note in Section 4-4, DFT Economic Analysis.

#### Step 1.

A set of requirements templates was completed for the design, manufacturing, and field deployment project phases. The purpose of using templates to specify requirements was to unequivocally define requirements quantitatively and to define metrics which would establish whether conformance could be established for a given requirement.

An annotated template establishing the requirement for "Detection coverage for design flaws" along with annotations which describe the individual entries is shown below. It is typical of the templates for all project phases.

#### Requirement Name : Detection coverage for design flaws Realizable \_\_\_\_\_ Consistent \_\_\_\_\_ Valid \_\_\_\_\_

#### a. Test Phase

• Design Phase selection by definition.

#### **b.** Test Means

- Simulation

- BIST

- BS-based ATE

- Non-BS-based ATE

- Manual procedures

These are the selected ordered set of test means available for detecting design flaws. Simulation is the primary method at the modeling level. Other means apply to the design phase up to and including production of the first prototype hardware. As will be seen in Step 7 where test requirements are finally consolidatedlater, the last four test last means belong to the STP. Simulation is a supplemental test means appropriate to the design phase. These test means are assigned independently by the expert representing the particular project phase, in this case **Design**.

#### c. Test Mode

• Off-line

The design phase is a non-operating test.

#### d. Degree of Allowable External Support

• Unlimited

No limitation is made since any available technician and/or engineering support will be made available to support the design effort.

#### e. Fault Model Assumption

• Design flaws : partitioning, interface, timing, model, algorithm

The listed set of design flaws are typical of a board design project.

#### f. Quantitative Definition of Metric

• Total number of design flaws detected, by divided by the total number of design flaws

This ratio defines the effectiveness of the design process.

#### g. Prediction and Validation Weighting Factors

• Flaw distribution profiles

Previous experience with board design processes establishes a likely distribution of similar flaws on future projects. These factors represent the capability of a specific companyCompany with a specific type of project.

#### h. Quantitative Requirement

• 99%

This number must approach 100% for a reasonable design process. Some tolerance must also be allotted to reflect the potential for an imperfect process.

#### i. Allowable Requirement Compliance Tracking Methodologies

- P analysis rate of flaw discovery

- V simulation (testbench, functional, mission)

- M data collection and statistics

Prediction of design flaws is based on analysis of the circuit function and the typical rate of discovery of flaws for a circuit of that type. Fewer flaws per unit time will be uncovered as the design approaches its completion.

Simulation is the primary design analysis tool. Lack of design flaw effects during simulation establishes the capability of a design. The rate of discovery during simulation can be compared with the predicted values for a consistency check.

The ultimate means of compliance tracking is actual measurement of performance of a design. A design performing as expected indicates the absence of design flaws.

#### Step 2.

Templates showing coverage for inherited anomalies were added to ensure that noany design flaw escapes (non-detections) from design to manufacturing and field phases or manufacturing faults from the manufacturing to field phase were accounted for. This coverage is added to reflect such possibilities and their effects upon satisfaction of the requirements. The possibility of inherited anomalies generally reduces the levels of detection, isolation, and correction which can be achieved by any real physical system.

#### Step 3.

An effort was made by each of the project-phase-specific representatives to examine the extent to which flaws/faults (titles of templates) in their respective areas could be "merged" so that the number of templates wais minimizreduced. This was

accomplished by searching the requirements templates for commonality among test means, support requirements, test mode, and quantitative requirements for the baseline set of flaws/faults established by that expert. This within-phase flaw/fault consolidation was performed independently for each of the phases of design, manufacturing, and field support. As flaw/fault consolidations occurred, the fault model entry (template entry e.) would bere modified to reflect the extension of coverage. and Iindividual quantitative requirements were explicitly specified as needed to document the post-merged results and preserve the established quantitative requirement values. Consolidation never eliminates important established requirements but may combine them. For BM3, an example of a fault merge is the template for "Detection coverage for manufacturing faults - Bridging, Open, and Stuck-At".

#### Step 4.

Following the within-phase flaw/fault consolidation, the test means for the identified coverages for **detection** and **isolation** within each test phase were examined for commonality with the intent of establishing a candidate local (within-phase) singular test philosophy (STP). For BM3 the test means subseries : BIST, Boundary Scan ATE, and standard ATE wereas appropriate. BIST and Boundary Scan-based The first two testing means weare very cost effective from the life cycle point of view and theseir tests weare executed in the shortest times. These tests are introduced during early simulations and, once developed, accompany the product through the manufacturing and field deployment phases. The need for specialized manufacturing or field testing is reduced or eliminated.

ANeeded additional coverage needed in any phase for a specific flaw/fault could be provided by supplementing the core test means set with flaw-/fault-specific test means. Inherited flaws/faults were not considered in the search for an STP to prevent forced commonalities from having an excessive biasing influence (feedforward or feedback) on any candidate STP. Correction is not included as a comparison category, since correction is almost always a manual process.

At the end of this step, the requirements have been **merged by test means within their respective life cycle phase**s. Three phase-specific candidate STPs exist.

#### Step 5.

Examination of the sets of test means applicable to the individual phases will exhibit the likelihood of obtaining a true STP **across all phases** at this point. Commonality will lead to a merging of the sets of test means across the phases. Lack of commonality will indicate that a singular test philosophy may not exist. In most cases, the extent of an STP derived at this point will be a core STP which may need supplementationg within individual life cycle phases. Results of the attempt to generate an STP may be any of the following cases :

- An STP can be formulated across all life cycle phases.

- A baseline for an STP can be established and applied across all phases if additions, deletions or reorderings of test means can be accomplished.

- Individual templates can be arbitrarily modified to conform to the STP.

- Individual templates can be tagged as not compatible with the preliminary STP.

The first two cases represent situations where an STP can be readily defined. **For BM3, the second case applied**. In all but a few instances, the original assigned ordering of in-phase test means in the templates was very similar and it was relatively easy to reorder the individual test means sequence for a specific nonconforming flaw/fault to bring their final ordering into conformance with the majority of the test sequences. Thus, the basis for a core STP was found.

In a few cases, the core set of test means was supplemented with appropriate means. In particular, INSPECTION was added as the first test means for manufacturing to consider the reality that a manual or assisted inspection should precede execution of BIST or any subsequent means when physical faults such as shorts or opens are the faults of interest. SIMULATION was added as a supplemental test means for design.

#### Step 6.

The STP was next applied to the inherited anomalies. For BM3, no significant problems were encountered and the STP was readily applied to the anomalies. Some reordering was required in a manner similar to that used in the across-phase consolidation.

For BM3, little effort was required in this area.

#### Step 7.

Final consolidation was achieved by taking the cross-phase STP and adding the supplemental test means as required.

For system test, the test means arrangement is : SIMULATION, BIST, BSCAN ATE, NON-BSCAN ATE, MANUAL

For manufacturing test, the test means arrangement is : INSPECTION, BIST, BSCAN ATE, NON-BSCAN ATE,

#### MANUAL

For field test, appropriate test means sets are :

At Organizational level:

o For inherited flaws/faults : BIST, MANUAL, MISSION OP

MISSION OP is added as a supplemental test means and corresponds to observation of the continued operational status of the equipment during mission operation.

• For all field faults : ONLINE CONCURRENT BIST, OFFLINE NONCONCURRENT BIST, OFFLINE BIST, MANUAL

In this case, the basic sequence is BIST, MANUAL to conform to the requirement that the equipment execute BIST during field deployment.

At Depot level :

BIST, BSCAN ATE, NON-BSCAN ATE, MANUAL

This arrangement is essentially the same as that for the manufacturing test since field Depot test corresponds to return to the manufacturing source for evaluation/repair.

The **core STP** is evident in all cases : BIST, BSCAN ATE, NON-BSCAN ATE, MANUAL

*Steps 8. and 9.* The STP was documented for BM3 by generation of a **Consolidated Requirements document**.

#### 4.2.4. Generation of TSDs and Test Architecture

The separate template sets, each containing the STP and any supplemental test means, were used to generate **test strategy diagrams (TSDs)** in their respective phases. The TSD is a two dimensional (see Figure. 3-1) array displaying fault coverage for detection, isolation, and correction for each of the test means used. Specific fault coverage for any test means is called the transfer function of the test and is the ratio of the number of successfully handled faults to the total number of input faults. Test costs and test times are also entered into the TSD as test attributes. Individual TSD arrays can contain requirements, prediction, verification, or measurement values, or differences between the cells of requirements and one of the other TSDs. A **prediction TSD worksheet** contains requirements, their predicted distributions, and the prediction minus requirement values in a specific RASSP project phase. The differences yield a quantitative statement of conformance to requirements. An EXCEL worksheet version of a requirements TSD for the FE at the subsystem level is shown in Figure. 4-3. At the architecture selection and definition phases, two coupled TSD arrays on the worksheet will contain experience-based predictions and differences between the requirements and predicted values. As the project advances, and simulations develop and measurements made on hardware become available, TSDs contained on other worksheets of the EXCEL workbook are created to measure simulation and hardware conformity to requirements.

# EXCEL TSD Example

| ol Nan  | IOW                 | 1           | 10       | ±                      | BZ         | U       | ===                    |             | \$ 9         | 6, :                   | 8 .2    | :::     | 1                      | <b>1</b>       |      |                        |                 |   |

|---------|---------------------|-------------|----------|------------------------|------------|---------|------------------------|-------------|--------------|------------------------|---------|---------|------------------------|----------------|------|------------------------|-----------------|---|

|         |                     |             |          |                        |            |         |                        |             | 1050         |                        |         | 0.55    | 8>12                   | >              |      | 80                     | 2               | 5 |

| V34     |                     | ±           |          |                        | -041204108 | 0.04440 |                        | Constants.  |              | 0000000000             |         |         |                        |                |      |                        |                 |   |

| 1000    | 19.22               | 5           | 102.65   | E DDIDI                | SINC OP    | епи     | CK-AT FAL              | II TE LIAN  | ,<br>01 CD C | INDINC N               | ONLIGOC | TIPIN   | TEET                   | Concerning and | 1.0  | 100 A 100 A            | 1000            | 2 |

| eter No | gaires e            | HL COR      | llowe of | . Statestes            |            |         | UNABLE PAL             |             | ULEU L       |                        |         | TO SHOE |                        | 1              |      |                        |                 |   |

|         | Filaw Pe            | ip. i.e. BR | IDGING   | , OPEII, \$1           | IUCK-AT    | FAULTS  |                        |             |              |                        |         |         | PHECA<br>Mainta        | 1              |      |                        |                 |   |

|         |                     | 1000.00     |          |                        |            |         |                        |             |              |                        |         |         |                        |                |      |                        |                 |   |

| tection | - 1                 | 65.002      | 380.0    | 10.002                 |            | 015.0   | 40.002                 |             | 155.00       | 50.002                 |         | 84.5    | 50.00Z                 | _              | 41.0 | 95.26%                 |                 |   |

|         | and Kines           | 18.4        |          | Test Year              |            |         | Test Time!             | 98.6        |              | Test Vine              |         |         | Test Time              | 26.1           |      | Teel line              | 998.5           |   |

|         |                     | 650.0       |          | Tel Set                | 35.00      |         | Teal Gal               | 126.00      |              | Trai Sad               | 94.50   |         | Test Cast              | 47.25          |      | Teel Coal              | 105             |   |

| olation | - 1                 | 35.00Z      |          | 20.002                 | 20.002     | 54.00   | 40.002                 | 40.002      | 138.00       | 50.002                 | \$0.002 | 101.3   | 50.00Z                 | 50.002         | F4.0 | 39.40%                 |                 |   |

|         | ent Winer           | 18.6        | 32.5     | Teal Time              | 20.002     |         | Test Time              | 40.002      |              | Test Vier              | 11.44   |         | Test Time              | 50.00.2        | •    | Test line              | 988 S           |   |

|         |                     | 611.5       |          | Tell Set               | 10.50      |         | Teal Cast              | 10<br>73.00 |              | Trai Sad               | 101.95  |         | Teal Cash              | 14,95          |      | Teel Coal              | 402             |   |

| methe   |                     | 0.002       | 610.     | 0.002                  | 0,002      | 601     | 0.042                  | 0,002       | 700          | 0.002                  | 8,002   | 501     | 100.002                | 100,002        |      | 100.00%                |                 |   |

|         | ral line            | 8,082       | 010      | Teal Time              | 0.004      |         | Teal Time              | 0.004       |              | Trail Line             | 0.004   | •       | Trail Diar             | 1058, 14       | •    | Trol Har               | -951 B.<br>11-9 |   |

|         | al Cal              |             |          | Trail Gast             | - 1        |         | Trail Coali            | - 1         |              | Teal Cash              | , a     |         | Teal Cast              | 910<br>878.5   |      | Test Cost              | - 119           |   |

|         | TIMS DE             | CTION 1     |          | BIS                    |            |         | ±<br>                  | TTE         |              | A                      | F       |         |                        | AN             |      | TOTAL                  |                 |   |

|         | ral Har<br>sel Cast | Cause       |          | Teal Time<br>Teal Coal |            |         | Teal Time<br>Teal Cost | 34.1        |              | Teal Time<br>Teal Carl | 30.8    |         | Teel Time<br>Teel Cert | 00.1           |      | Teal Blac<br>Teal Cost | 3736.66         |   |

|         |                     |             |          |                        |            |         |                        |             |              |                        | tene    |         |                        |                |      |                        |                 |   |

|         |                     |             |          |                        |            |         |                        |             |              |                        |         |         |                        |                |      |                        |                 |   |

|         |                     |             |          |                        |            |         |                        |             |              |                        |         |         |                        |                |      |                        |                 |   |

|         |                     |             |          |                        |            |         |                        |             |              |                        |         |         |                        |                |      |                        |                 |   |

| ig. 2.3 | 3.2.2-              | 3a, BM      | IS TSI   | D1 Shee                | 9t 1 - R   | equin   | ements                 | TSD fo      | r =E         |                        |         |         |                        |                |      |                        |                 |   |

|         |                     |             |          |                        |            |         |                        |             |              |                        |         |         |                        |                |      |                        |                 |   |

|         |                     |             |          |                        |            |         |                        |             |              |                        |         |         |                        |                |      |                        |                 |   |

Figure 4 - 3: TSD for open, short, and bridging faults for manufacturing test of BM3 FE.

For BM3, requirement/prediction TSDs for selected flaws and faults during design, manufacturing, and field deployment were produced for the FE as a **subsystem** and for the FE divided into its three **PC board** (one FPCTL, two FPCAP) constituents. Other TSDs could have been generated, but the handling of these fault classes were well understood, so and standard fault management control techniques would bere applied. **TSDs are used to their best advantage to specify/monitor coverages for faults not fully understood.**

#### 4.2.4.1. TSD Transfer Function Values

TSD Transfer Function Values A transfer function is a quantitative specification of detection, isolation, or correction coverage by a specific test means. Specific parameter values assigned to test means in the BM3 prediction TSDs were based upon historical experiences with similar projects. As an example, consider the case of short circuit faults:

INSPECTION - detection 65%, isolation 95%, correction 0% - based on the assumption of a multilayer board and experience with inspection of similar boards. An estimate of the number of visible traces vs. the total number of traces is a good starting point for detection. The 95% isolation value is selected since detection implies that isolation has been accomplished. The 0% correction allocation is assigned here since correction is not a normal function of an inspector.

BIST - detection 10%, isolation 20%, correction 0% - Values for this test means are low since the FPCTL board contains only 2 components (of 15) with an incompletely understood BIST capability. A reasonable assumption for is to assign the BIST values based upon the percentagefraction of circuitry which contains BIST. Correction

receives a 0% value since BIST will not change conditions causing a short fault.

BOUNDARY-SCAN ATE - detection 40%, isolation 40%, correction 0% - BS-ATE is assigned a relatively high value for detection since BS-ATE can detect short faults as well as faulty components in the interconnection paths. The actual values are chosen by examination of the interconnection routing and an estimate of the percentagefraction of the board circuitry accessible to BS-ATE testing. Isolation is given the same value as detection since BS-ATE testing is intended to locate faults by proper choice of test vectors. BS-ATE does not perform correction, thus the 0% value for this transfer function.

NON-BS-ATE - detection 50%, isolation 50%, correction 50% - Non-BS ATE is testing on an external tester. The detection level possible below the related to the number of traces/components which are accessible via a test connection interface such as bed-of-nails. Isolation for non-BS ATE testing is assumed to be theat same as for detection. Correction is given a value of 0% for this test means for FPCTL.

MANUAL TEST - detection 50%, isolation 50%, correction 100% - Detection and isolation are assigned estimated values based upon the nature of the testing anticipated. Values assigned reflect the ability of a "typical" manual test to identify and locate a specific fault causing the problem reported by a previous test means. Manual test is expected to be used mainly as a path to **correction**. It is not intended to be a primary means for detection of faults because the **time consumed by a manual test as a primary test means for detection and isolation is long and such a test is costly**. Correction is assigned a value of 100% - otherwise the board under test is declared non-functional.

Similar lines of reasoning were used to assign other transfer functions used in TSDs. The resulting values were **assumption-based**. Their use will allowed reasonable allocation of expected values for detection, isolation, and correction events. The **assumptions used can be modified** to conform to a particular companyCompany's capability to execute the testing required. For example, if a company does not have non-BS ATE, it cannot execute such a test and either the available means must perform more effectively or other additional test means must be made available to replace the "missing" capability.

#### 4.2.4.2 TSD Test Time/Test Cost Attribute Values

TSD Test Time/Test Cost Attribute Values Test time entries for TSD attributes are based primarily upon estimates of the time required for test means with generic characteristics to complete a specified test. BIST, for example, is typically completed in microseconds or milliseconds, and manual tests typically take tens of minutes to complete. Known values are used if available but this situation rarely occurs during a test design phase. The exact number of microseconds or minutes is not critical. The order of magnitude will categorize the time and cost for a test means. Most test cost/time analysies will thus be **assumption-based** and will use results reported by experienced test experts familiar with similar tests to generate cost/time attributes.

Test cost entries for TSD attributes come from estimate of the **fixed** and **variable** costs associated with testing. Fixed costs are based on the cost of test equipment needed to test all boards produced, fixturing costs and nonrecurring labor cost for test development. Variable test costs are associated with technician labor required to perform tests. The amount of labor required is directly related to the test time discussed in the previous paragraph.

#### 4.2.4.3. TSD Implementation

The TSD sets for BM3 were constructed as **EXCEL workbooks** designed to efficiently implement data sharing among all the two dimensional spreadsheets in the set. Each workbook consists of a set of worksheets which details the four classes of TSDs for one particular flaw or fault.

Three worksheets form a set capable of controlling/monitoring of a specific flaw/fault. A separate workbook is assigned to each flaw and fault for which requirements have been established. Individual worksheets are assigned to requirements, predictions, verification, and measurement related to the flaw/fault. For any one complete workbook, the number of worksheets will be up to 12. At system design levels, fewer sSheets will be needed since verifications and/or measurements may not apply.

During the system concept and design development phases of a project, the requirements and prediction worksheets are populated. Verification and measurement worksheets will be populated as the project proceeds into the actual design and fabrication phases.

Figure 4-4 identifies the contents on the worksheets for one TSD class (requirements, prediction, verifications, or measurements) in one EXCEL workbook. For the sake of analysis, a **Rrequirements TSD set** will be discussed.

Figure 4 - 4: Worksheets for an EXCEL Test Strategy Diagram set.

Sheet 1 contains a flaw/fault specific TSD which states the **requirements** for testing related to that flaw/fault at some level of packaging. On this sheet, the user will enters the transfer functions, cost and time allocations appropriate to the flaw/fault being processed.

Sheet 2 contains a Rroll-up **requirements** TSD for a specific flaw/fault and the allocation of these requirements among the contributing lower packaging levels. For example, a TSD describing **subsystem** requirements will have **board** components. Downward allocation ensures that each lower level packaging level is examined to ensure that it will satisfy requirements which must be met in order that the requirements of the higher assembly be satisfied. The roll-up is the topmost section of Sheet 2. The roll-up TSD is automatically created from summing the contributions from the individual lower level TSDs.

TSDs at different packaging levels are coupled by EXCEL intersheet and inter-workbook communication. Thus the roll-uprollup TSD from a lower level TSD can function as a complete Sheet 1 entity at some higher packaging level.

Sheet 3 contains the differences between the **requirements** stated on Sheet 1 and the **roll-up section** of Sheet 2. Sheet 3 entries are **automatically generated** by intersheet subtraction. During system design phases, reported differences between requirements and predictions could suggest that there could be a problem with the requirements.

Similar sets of TSDs for the same flaw/faultcan be constructed to specify reporting means for verifications and measurements. The TSD set thus serves as the common connection link among requirements, predictions, verifications, and measurements and specifies values for detection, isolation, and correction for each of these categories.

#### 4.2.5. Test Pprocedure Development

Test procedures are defined once the physical test setup has been established and a test plan has been designed. Both the plan and procedures are outputs of **test architecture** (TA) design and TSD construction. The TA is constructed simultaneously with the TSDs since any evolving test strategy needs an infrastructure which can support the tests called for in the TSD. In particular, all testbenches must be built using test features which will be physically realizable. BIST and JTAG test elements become embedded into testbenches and the extent to which these features are used impacts the entire test environment. Testability features themselves are tested during simulation. BIST and Boundary Scan testing are desirable but they are only supportable by designs containing BIST circuitry or JTAG-compliant components.

Also, any testing requires access to the physical testers required to perform the tests. If expensive ATE is currently not available, either it must be acquired or the test strategy calling for its use must be modified. For any company, a one-time analysis of facility test equipment in terms of expected project needs should be performed to ensure that the test architecture required to support test plans is appropriate. The analysis for BM3 generated a list of test means available to Lockheed Martin to evaluate different potential equipment anomalies. Tests selected for the STP were chosenselected from this list based upon availability of specific test means.

When all the details of test architecture are resolved, a test plan which orders application of test means in accordance with the TSDs is generated. For the BM3 exercise, BIST and Boundary Scan test were used as primary test means even though the FPCTL board was not built using a majority of BIST or JTAG components. (Customer requirements demanded use of these test means.) BIST and Boundary Scan test were augmented with the use of a wide range of test means at the disposal of the LM facility. Test procedures were developed in template form to provide test personnel with a well defined test sequence and a statement of all required test data.

#### 4.2.6. Board Level Application of DFT Design Tools

DFT installation is supported by several tools which add DFT features to ato a design and evaluatesexaluate their effectiveness of the addition. Most of these were VHDL-based, which is in line with the use of VHDL as the basic RASSP modeling language.