### Model-Based Design for Altera FPGAs Using HDL Code Generation

Z

© 2011 The MathWorks, Inc.

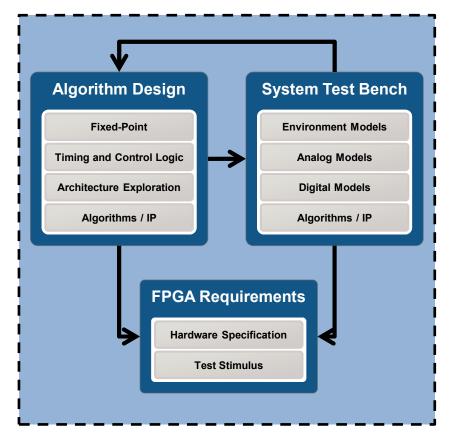

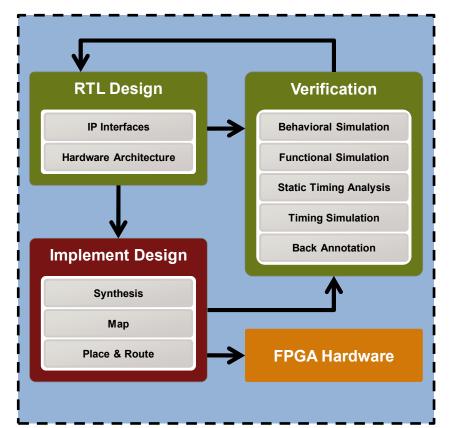

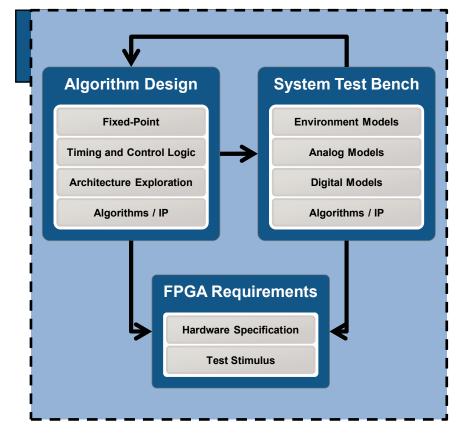

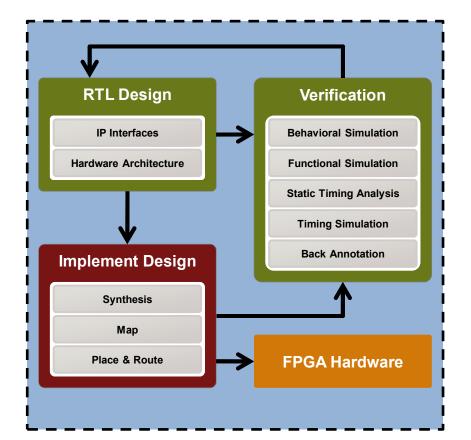

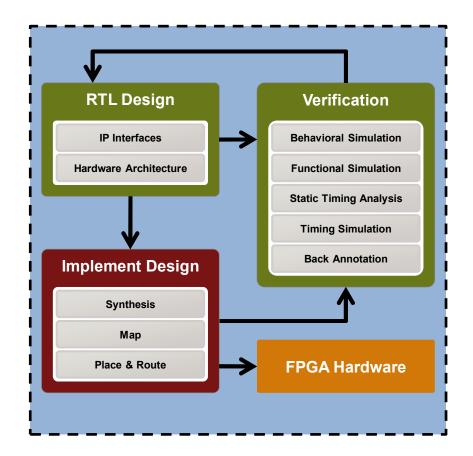

## **Separate Views of DSP Implementation**

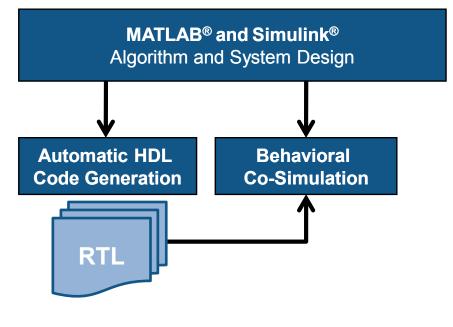

#### **System Designer**

#### **FPGA** Designer

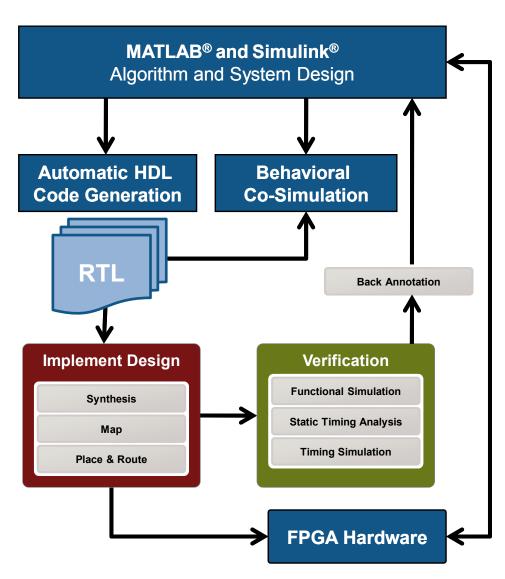

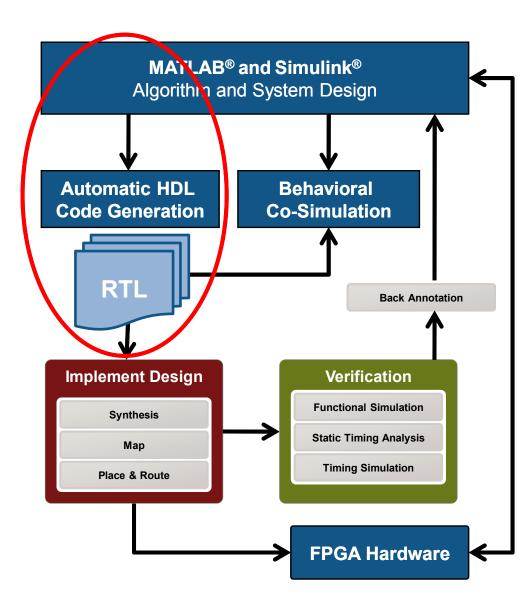

**MATLAB® and Simulink®** Algorithm and System Design

Automatic HDL Code Generation

**FPGA Hardware**

Faraday Accelerates SIP Development and Shrinks NAND Flash Controller ECC Engine Gate Count by 57%

#### Challenge

Accelerate the development of SoCs and ASICs

#### **Solution**

Use MathWorks tools for Model-Based Design to speed up system-level simulations, improve system performance, and shorten time-to-market

#### Results

- Simulations 200 times faster

- Throughput performance increased by 15%

- Gate count cut by 57%

Faraday's silicon IP on an SoC.

"The Simulink environment is ideal for system-level architecture exploration. The simulations are 200 times faster than they were in our previous workflow — and Simulink models can be easily converted to C as well as to HDL code, which enables high scalability and reusability."

> Ken Chen Faraday

#### From Algorithm to Synthesizable RTL

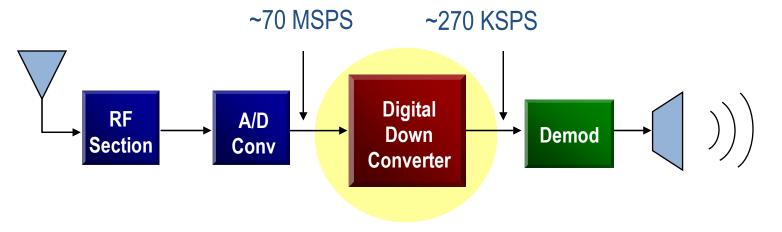

#### **Digital Down Converter**

#### DDC accepts

- A high sample-rate passband signal (may be 50 to 100 Msps)

- DDC produces

- A low sample-rate baseband signal ready for demodulation

Find and fix issues

#### **Fixed Point Analysis** Digital Down Converter

Run

Name

Contents of: Lowpass Filter

Column View: Simulation View

Stage6 : Product output

III Stage6 : Accumulator

Stage5 : Accumulator

III Stage4 : Product output

Stage6 : Output

Stage5 : Output

Results

20 K

---

View

Tools

Help

Show: Min/Max results

SimDT

fixdt(1,48,48)

fixdt(1,18,16)

fixdt(1,48,47)

fixdt(1,30,48)

fixdt(1,18,16)

fixdt(1,48,47)

fixdt(1.48.48)

Fixed-Point Tool

🕕 💿 🔛

Collect Autoscaling

m02 ddc fixedpoint\*

Spectrum Processing

ddc fixed point (mn

Lowpass Filter

🖄 DDC Spectrum

IF Source1

DT DT

File

Model Hierarchy

₽\$

╘┓

ষ্ঠ ddc

₽₿

- Convert floating point to fixed point models

- Automatic tracking of signal range (also intermediate quantities)

- Fraction lengths recommendation

- Bit-true models in the same environment

- Quantify the impact of fixed point quantization

•

Run

Active

Active

Active

Active

Active

Active

Show Details

Active fixdt([],30,48)

SpecifiedDT

fixdt([],48,48)

Same as input

Same as input

fixdt([],48,47)

fixdt(0.48.48)

fixdt([],48,47)

SimMin SimMa

-3.946... 8.7189

-1.892... 3.6209

-9.857... 9.9699

-0.262... 0.262

-3.051... 0

-1.525... 0

| ation                   | with fixed point<br>easily                                                                                                                                 |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | 7/                                                                                                                                                         |

| ax Des Des Overflowy ps | Current System: Lowpass Filter       Current system settings       Saturations       Fixed-point instrumentation mode       Controlled by: ddc_fixed_point |

| )<br>5 6580             | Data type override:<br>Use local settings                                                                                                                  |

| )                       | Data collection                                                                                                                                            |

Simulate model and store res

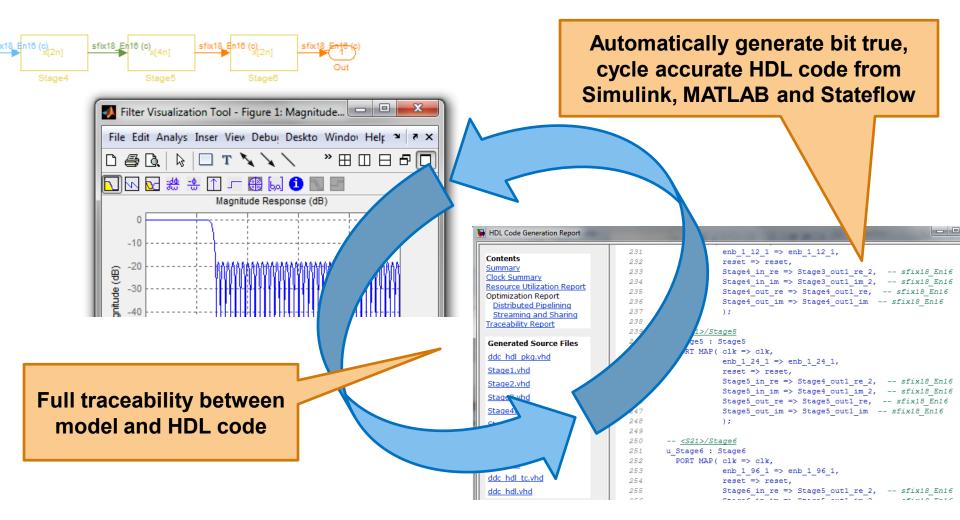

#### Automatic HDL Code Generation Digital Down Converter

#### **Integrated HDL Verification**

## Verification Challenges: HDL Verification

- Design the Test Bench twice

- 10 to 1 ratio of Test bench LOC to Design LOC

- Many stimulus files from MATLAB

- These are ideal references which require pre- and post-processing

- How to analyze results?

## Verification Challenges: HDL Verification

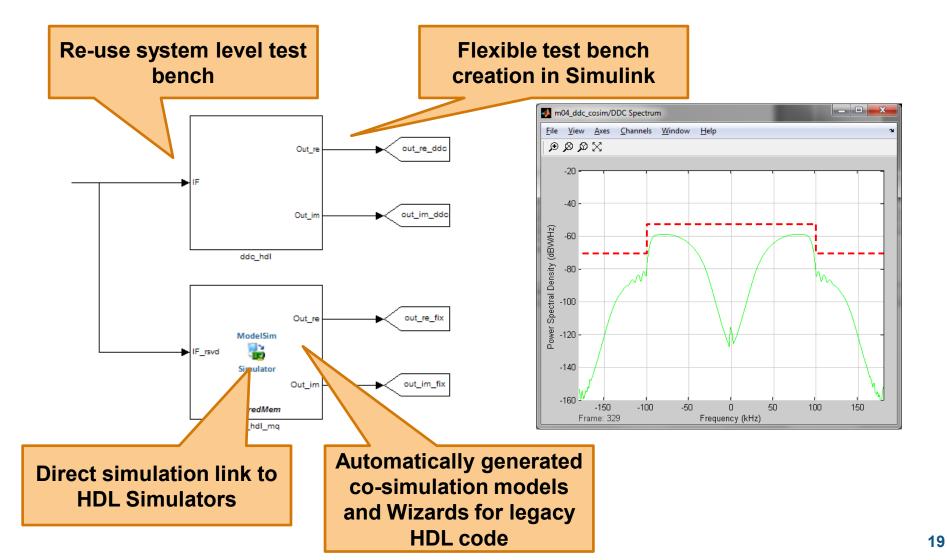

## **Demo: Re-Use System Level Test Bench**

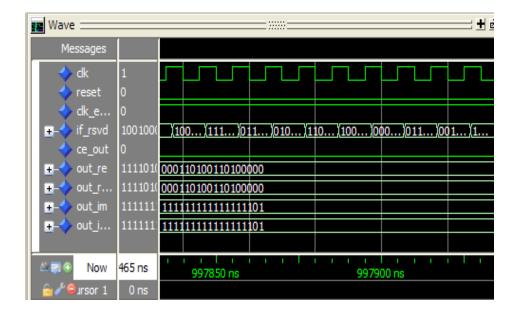

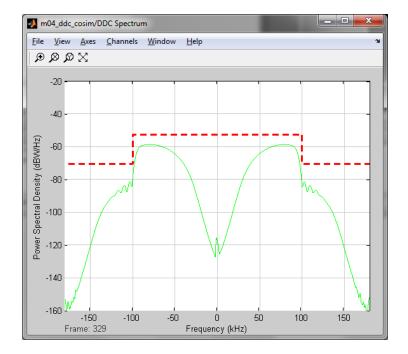

## **Co-Simulation with HDL simulators Digital Down Converter**

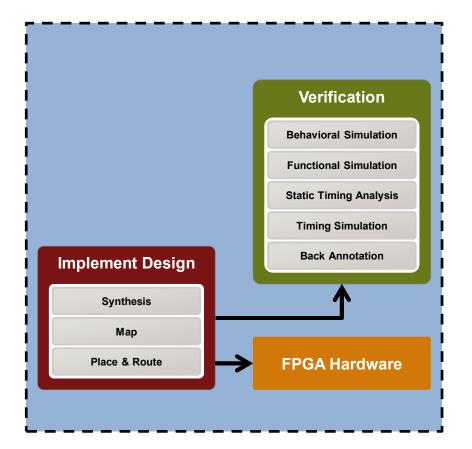

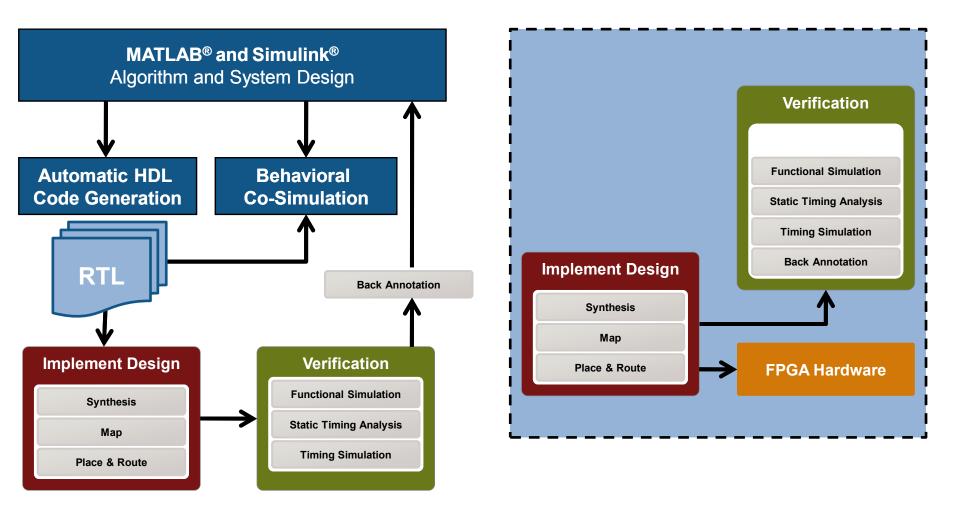

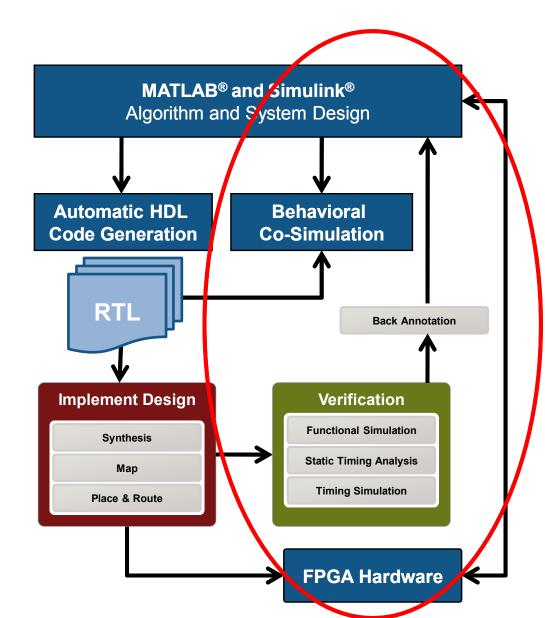

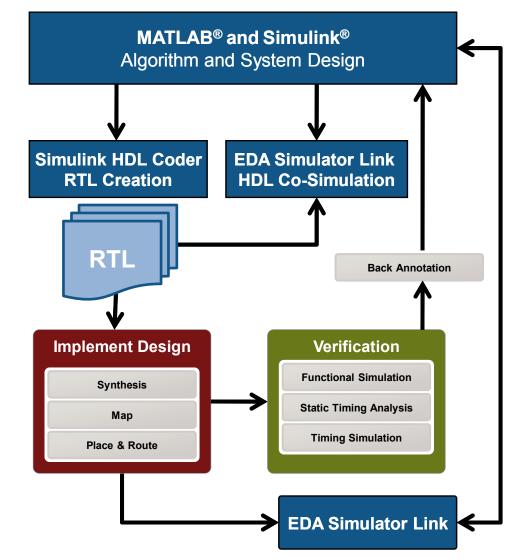

# From Algorithm to FPGA Prototyping and Verification

#### Next Steps ...

1. Visit <u>www.mathworks.com/fpga</u> for more information

- 2. Watch our FPGA webinars: <u>mathworks.com/company/events/webinars</u>

- Contact your local sales reps for a <u>trial</u> of MathWorks HDL code generation and verification products

| MathWorks <sup>.</sup>                               | Accelerating the pace of engineering and actence Select Country V   Contac                                                                                                                                                                                                                                                                                                                                                                                                                      | Eric Cigan   My Account   Log Out                                                                                              |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| ucts & Services Solution                             | is Academia Support User Community Company                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                |

| 3A Design Overview<br>nos and Webinars<br>rr Stories | MathWorks FPGA Design Solutions - FPGA Design                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                |

| ning                                                 | FPGA Design Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Contact Sales                                                                                                                  |

| nical Literature                                     | MathWorks FPGA Design Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Trial Software                                                                                                                 |

| ts                                                   | Using Simulink with Altera DSP Builder                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Free Technical Kit                                                                                                             |

|                                                      | Using Simulink and Simulink HDL Coder with Mentor Graphics FPGA Design Tools                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                                              |

|                                                      | Using Simulink with Xilinx System Generator for DSP<br>With Simulinik, algorithmic blocks, and legacy HDL code, you create a system-level model of your<br>design and elaborate the design to prepare for hardware implementation. Simulink HDL Coder™                                                                                                                                                                                                                                          | Lockheed Martin<br>Space Systems                                                                                               |

|                                                      | lets you automatically generate HDL code for rapid implementation of algorithms in FPGAs. You<br>can functionally verity your HDL code by using EDA Simulator Line** to connect a Simulink test<br>bench with your FPGA implementation running in an HDL simulator.                                                                                                                                                                                                                             | visualize the operation of the<br>system as it was running, and the<br>model served as a golden<br>reference for the hardware. |

|                                                      | Model and Simulate Algorithms for Implementation on FPGAs<br>Designing algorithms for implementation on either FPGAs or FPGAs combined with processors                                                                                                                                                                                                                                                                                                                                          | Additionally, EDA Simulator Link<br>proved invaluable for continuously<br>verifying the accuracy and                           |

|                                                      | requires accurate modeling of fixed-point characteristic that affect functional performance. You<br>can create floating-point algorithms specifications in MATLAB and Simulink and then convert them<br>to bit-ture, fixed-point data types for simulation. Elaborating your design in fixed point at the                                                                                                                                                                                       | validity of the design and for<br>troubleshooting any anomalous<br>behavior observed in the hardware.                          |

|                                                      | model level lets you thoroughly explore the fixed-point tradeoffs involved in FPGA design. You<br>can also create finite-state machines to model the control logic of these algorithms.                                                                                                                                                                                                                                                                                                         | » Read the story                                                                                                               |

|                                                      | ETRI Develops Modern Synchronization Technology for Fourth-Generation Mobile<br>exercises Telecommunications System                                                                                                                                                                                                                                                                                                                                                                             | Related Products<br>= EDA Simulator Link <sup>ns</sup><br>= Filter Design HDL Coder <sup>ns</sup>                              |

|                                                      | Generate Synthesizable HDL Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Fixed-Point Toolbox™ Simulink HDL Coder™                                                                                       |

|                                                      | With Simulink HDL Coder you can automatically generate outomizable, target-Independent VHDL<br>and Verilog code from your models that can be synthesized for FPGA implementation. You can<br>quickly motify the code by updating the model and regenerating the code. The generated code<br>can be passed to downstream tools for synthesis, placement, routing, and downloading of the                                                                                                         |                                                                                                                                |

|                                                      | bibitream onto an FPGA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                |

|                                                      | woher From MATLAB and Simulink to FPGAs in Five Easy Steps                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                |

|                                                      | Automate HDL Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                |

|                                                      | Reuse your Simulink model as the test bench to verify your FPGA implementation through<br>cosimulation. With EDA Simulator Link, you simulate your implementation in HOL simulators such<br>as ModelSim and use Simulink to reast simulus, ainutiate the golden netwence model, and<br>compare expected with actual simulation results. EDA Simulator Link lets you run batch regression<br>rests and conduct intreactive depolarging sessions using both Simulikar of your HOL simulator. This |                                                                                                                                |

## **Questions?**