# Design Once with Design Compiler® FPGA

The Best Solution for ASIC Prototyping

Synopsys Inc.

### Agenda

- Prototyping Challenges

- Design Compiler® FPGA Overview

- Flexibility in Design Using DC FPGA and Altera Devices

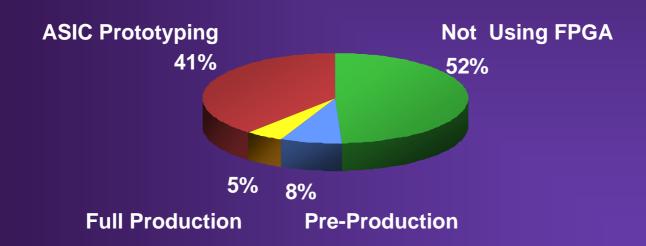

### 41% of our ASIC customers are prototyping their ASIC designs in FPGA

Synopsys 2004 Implementation Seminar Survey

Customer's use of FPGA's – Multiple Responses Allowed

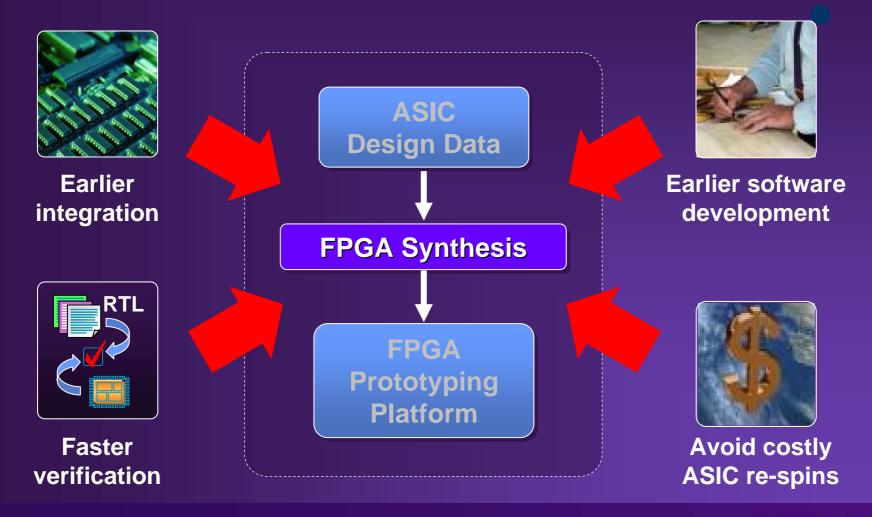

# Compelling Needs are Fueling Prototyping Market

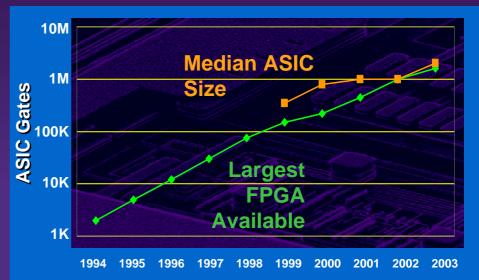

# ASIC Prototyping Poses Complexity Challenges

- FPGAs are approaching ASIC-like complexity

- Require ASIC-strength solution

- Timing Quality of Results is critical

- Many prototypes (such as, wireless) need to run at top speed

- Real World Interfaces do not slow down for prototypes

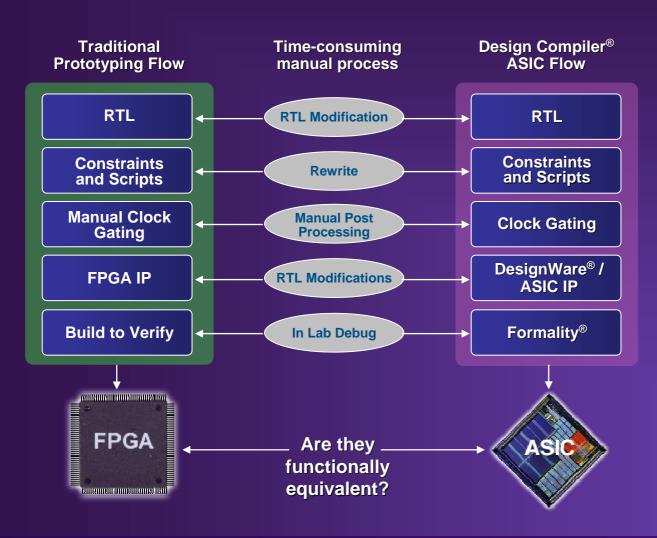

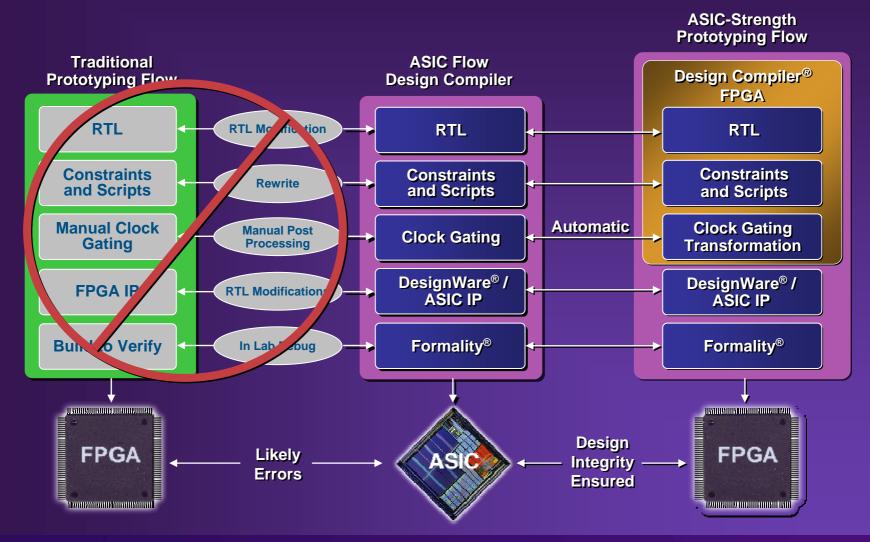

### Two Flows = Two Implementations

- Different source, tools, IP and flows

- Time consuming, error prone, manual modifications

- Is design integrity guaranteed?

### Agenda

- Prototyping Challenges

- Design Compiler® FPGA Overview

- Flexibility in Design Using DC FPGA and Altera Devices

### **Design Compiler FPGA**

**Evolutionary**

Revolutionary

Design Compiler®

**FPGA Optimized**

Adaptive

Optimization™

Technology

- Industry standard ASIC-strength solution

- Best timing

- Fastest path to prototype

### Industry Standard ASIC-Strength Solution Built on Design Compiler® Technology

- ASIC Reliability

- Proven through over 125,000 ASIC tapeouts

- Advanced

- Algorithms that deal with the most challenging designs

- Controllability

- Ability to customize the synthesis process to meet your design goals

- Formal verification support

- ASIC strength platforms

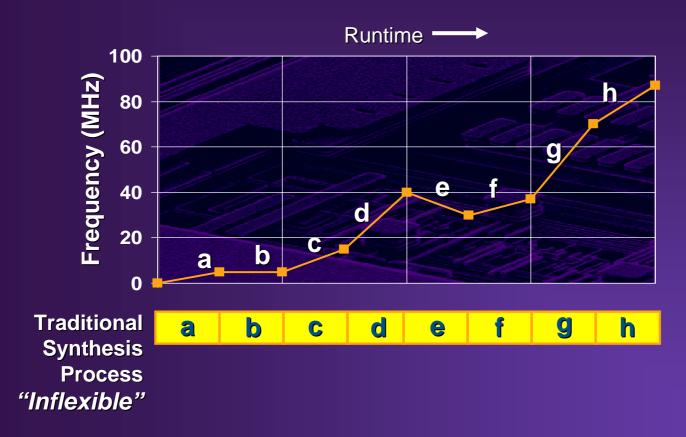

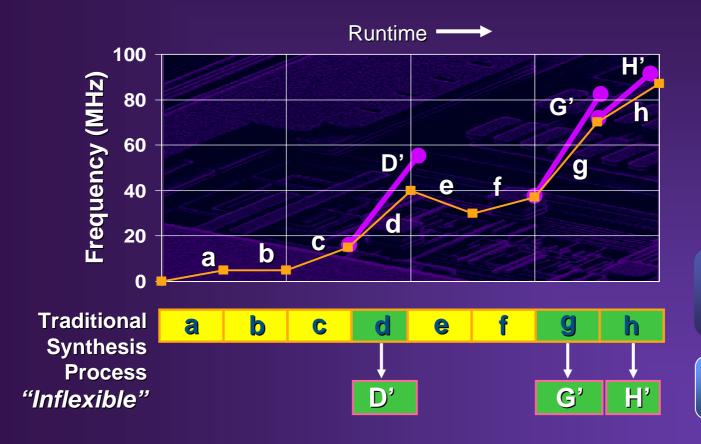

# Drawback of Traditional "Inflexible" Synthesis Process

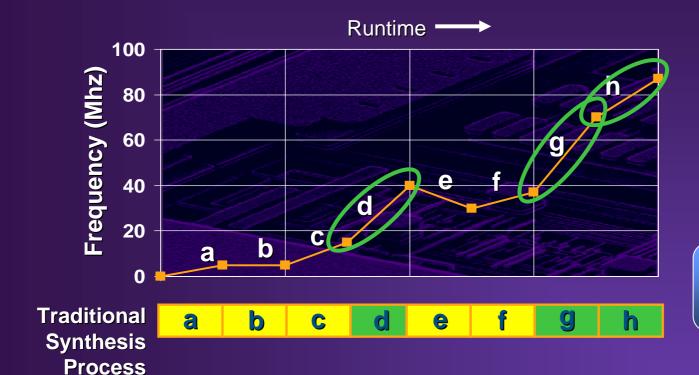

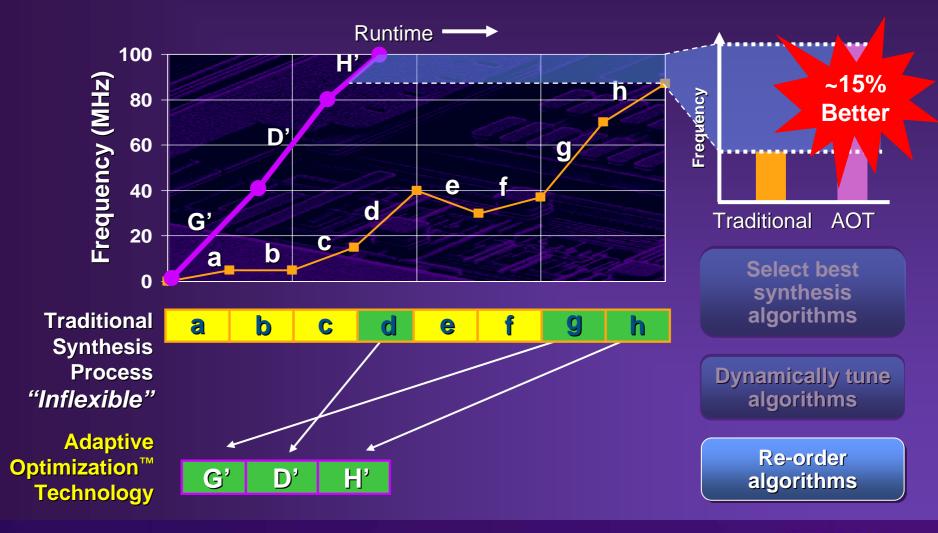

# Adaptive Optimization™ Technology Delivers the Best Timing

Select best synthesis algorithms

"Inflexible"

# Adaptive Optimization™ Technology Delivers the Best Timing

Select best synthesis algorithms

Dynamically tune algorithms

# Adaptive Optimization Technology Delivers the Best Timing

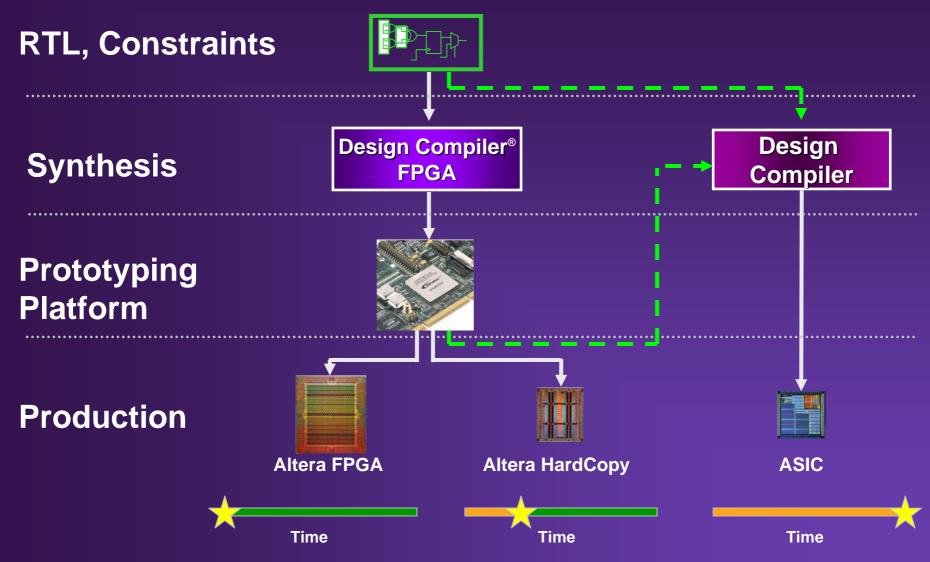

# Design Once With Design Compiler® FPGA

### **ASIC-Strength Flow at Alereon**

"The [DC FPGA] methodology and flow were exactly the same as Design Compiler so we were able to use the same scripts, constraints and RTL from the ASIC design."

- Dave Ohmann, IC Design Engineer

### **Best Timing at AMD**

"...A significant speed increase over what we were able to achieve with other FPGA synthesis tools."

- Dirk Haentzschel, Sr. Design Engineer

### Fastest Path to Prototype at Matrix Semiconductor

"Design Compiler FPGA was the <u>only FPGA</u>

<u>synthesis solution</u> that had an <u>integrated</u>

<u>ASIC/FPGA</u> flow, providing the easiest path to prototype our technology."

-James Tringali, ASIC Design Manager

#### Agenda

- Prototyping Challenges

- Design Compiler® FPGA Overview

- Flexibility in Design Using DC FPGA and Altera Devices

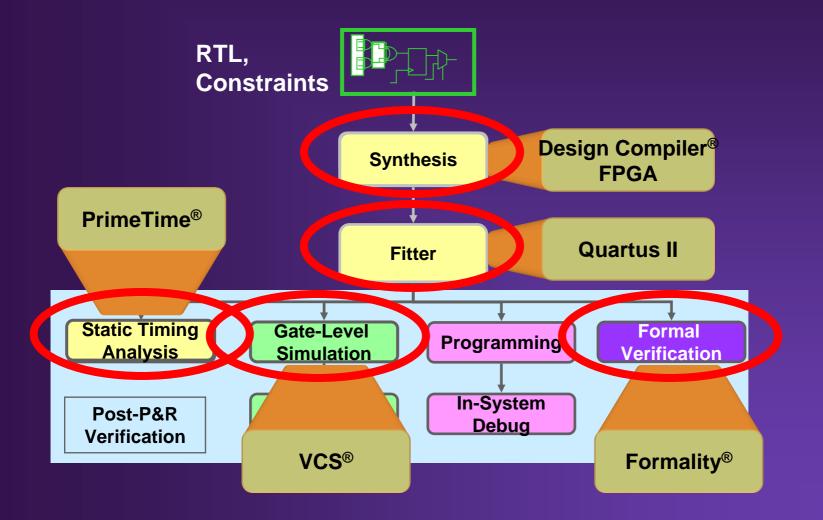

### **Design Once Implementation Flow**

#### **ASIC Strength Flow for Flexibility**

### Design Compiler® FPGA Supported Devices and Platforms

- Stratix™

- Stratix™ GX

- Cyclone™

- HardCopy™

- Stratix<sup>™</sup> II (Available 2004.12)

- Cyclone™ II (Available 2005.03)

DC FPGA is available today on: Solaris (32 and 64 bit) and Linux

### DC FPGA is Having Significant Success Over 80 Customers

ageresystems

Integrierte Schaltungen

### Fastest Path to Prototype DC FPGA Partners

**Automated Partitioning**

**DSP Algorithms in Silicon**

**Embedded Instrumentation**

**Hardware Assisted Verification**

**Configurable Cores**

**Reconfigurable Prototyping Platforms**

#### Summary

#### Design Compiler® FPGA

- Industry standard ASIC-strength solution

- Flexibility and Stability of DC

- Advanced Algorithms

- Best timing

- Adaptive Optimization™ Technology

- Fastest path to prototype

- Ensuring Design Integrity between Prototype and ASIC

- Flexibility to target Altera FPGA or HardCopy Devices

#### **Design Once!**