#### Timing-Driven Design for Optimal Area & Performance

October 2003

#### Synplicity Overview

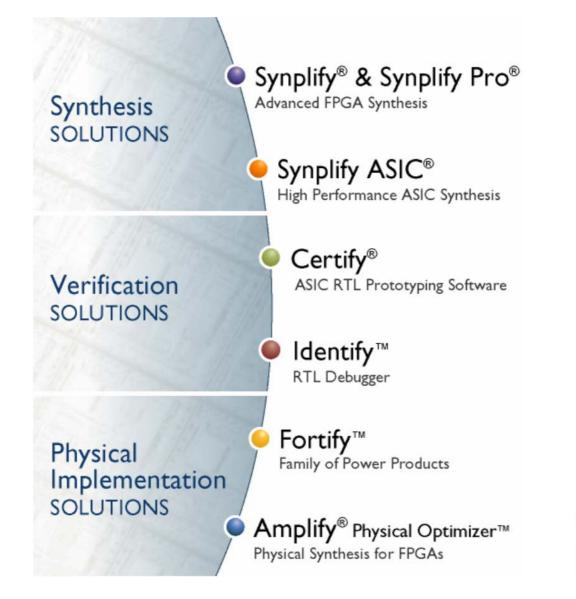

- Synplicity's Solutions

- Identify Demo

### Synplicity, Inc.

EDA software company founded in 1994

Unique company philosophy

- Best results don't have to come from hard to use tools

- Flexible and easy to work with company

- Dedicated to providing the best technical support

#### FPGA expertise

- Synthesis

- Physical Synthesis

- Debug

#### Simply Better Results<sup>®</sup>

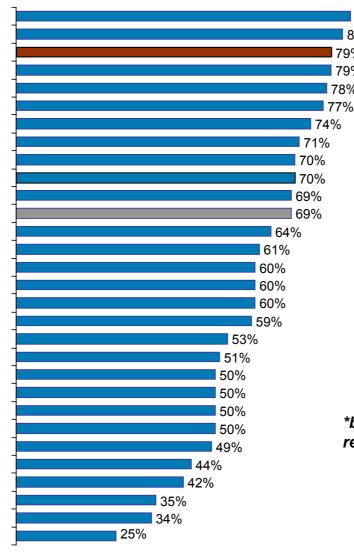

#### **Top Ranking in Customer Satisfaction**

Novas Software \*Get2Chip Synplicity **Verplex Systems Synopsys** Nassda **Mentor Graphics** \*0-In Design Automation **Cadence Design Systems** Denali Software Verisitv **Industry Average** \*Forte Design Systems \*Sequence Design Agilent EEsof EDA \*Ansoft \*Tera Systems \*TransEDA \*TannerEDA \*Magma Design Automation, Inc \*Analog Design Automation \*Axis Systems, Inc. \*Barcelona Design \*CoWare **Exemplar Logic** \*Summit Design \*Synchronicity \*Monterey Design Systems, Inc. \*Aldec Corporation \*Aptix

Customer **Satisfaction June 2003**

84% 82%

79%

79% 78%

> Base = # who have purchased or used a product from the vendor

\*base too small (20 or fewer responses); interpret data with caution

Synplicity<sup>\*</sup> **Simply Better Results**

#### **Synplicity's Design Solutions**

#### **Top FPGA Design Challenges**

As described by today's FPGA designers

- Achieving Performance Goals

- Timing Closure

- Productivity

- Debug

- Prototyping

#### Achieving Performance Goals (Synplify & Synplify Pro)

#### **Performance Goals**

Synplify (Mappers) are architecture aware

Optimizations are performed based on timing constraints

-Hierarchical boundary optimization

#### BEST algorithms extract high level components

- RAM's, FSM's, wide muxes, adders/multipliers, etc.

- -Technology-specific optimizations made *after* extraction

### **Set Proper Timing Constraints**

Synplify and Synplify Pro are timing driven

- Optimization decisions are made based on the timing constraints

- Not simply optimizing for performance or area

- Saves on device cost by using the smallest part while meeting your timing

#### Forward annotation to P&R

- Timing information is forward annotated to Quartus place & route

- More detailed and accurate timing constraints yield the best results<sup>20</sup> YEARS of

### **Basic Clock Options**

#### Frequency / Period

- Enter one (displayed in bold)

- Others are automatically derived (regular font)

#### Clock Group

- Default clock group: default\_clkgroup

- Only paths between clock domain from the same clock group are analyzed

- Use real constraints for your design don't over constrain

#### To optimize strictly for area set frequency to 1MHz

|   |          | Enabled  | Clock                        | Frequency<br>(MHz) | Period<br>(ns) | Clock Group      | Clock Rise<br>(ns) | Clock Fall<br>(ns) | Duty Cycle<br>(%) | Route<br>(ns) | Virtual<br>Clock |

|---|----------|----------|------------------------------|--------------------|----------------|------------------|--------------------|--------------------|-------------------|---------------|------------------|

|   | 3        | V        | clk3                         | 100                | 10.000         | D1               |                    |                    | 50                | 2             |                  |

| 4 | 4        |          | clk4                         | 83.333             | 12.000         | D1               |                    |                    | 50                |               | ☑                |

| • | <u>۱</u> | Clocks 🗸 | Inputs/Outputs 🔏 Registers 🔏 | Multi-Cycle Pa     | aths 🔏 Fal     | se Paths 👗 Attri | ibutes 🔏 Oth       | er /               |                   | •             |                  |

### **Advanced Clock Options**

#### Rise, Fall, Duty Cycle

- Use *Clock Rise/Fall* to specify rising and falling edges

- duty cycle automatically derived

- OR Specify the clock cycle as a % of the clock period

- rise reset to 0, fall automatically derived

- Default is Rise=0, Fall=period/2, Duty Cycle=50%

- Route

- Use to shrink the effective clock period without affecting the clock constraint forward-annotated to Quartus P&R

#### Virtual Clock

- Use for external clock signals clocking top-level ports

### **IP Support**

Altera Clearbox support allows Synplify to perform realistic timing analysis, optimizations, and reporting – Synplify Pro only

# Mixed language support Symplify Pro only

#### **Forward Annotation to Quartus**

- Timing constraints forward annotated to Quartus Place & Route

- Frequency

- Duty Cycle

- I/O Delay

- Multi-Cycle Paths

- False Paths & max\_delay path

- Clock Relationships

- Pin Assignments

- Accomplished through .vqm & .tcl

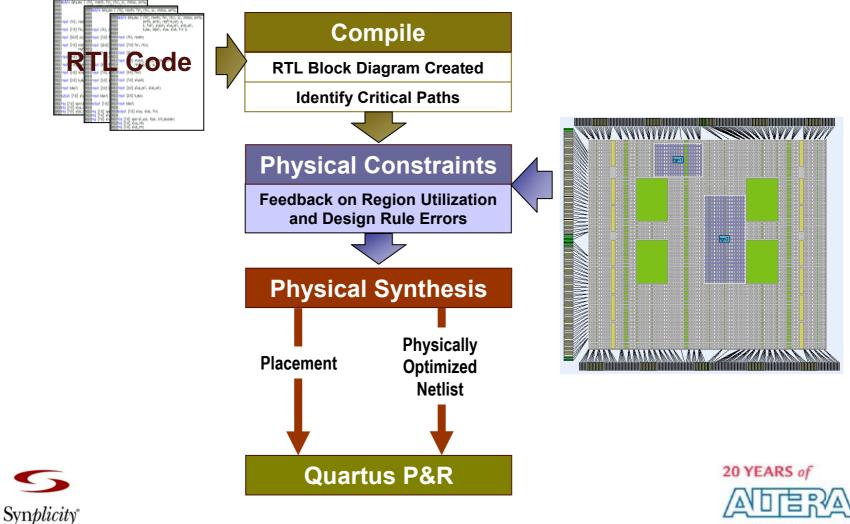

#### **Timing Closure** (Amplify Physical Optimizer)

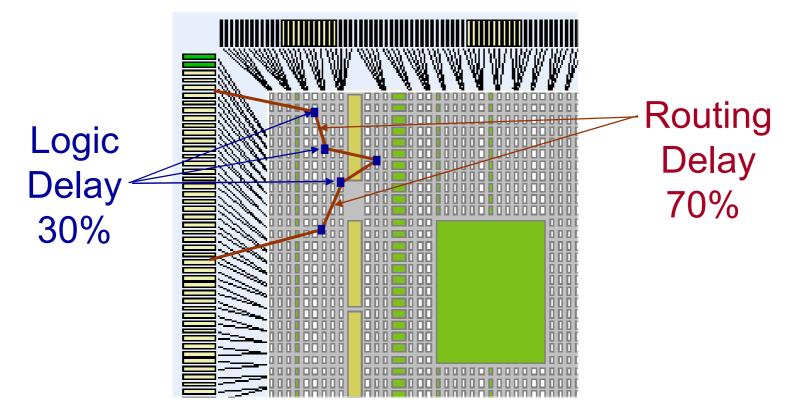

#### **Routing Governs Performance**

Must incorporate physical information into synthesis

The larger the design, the larger the problem

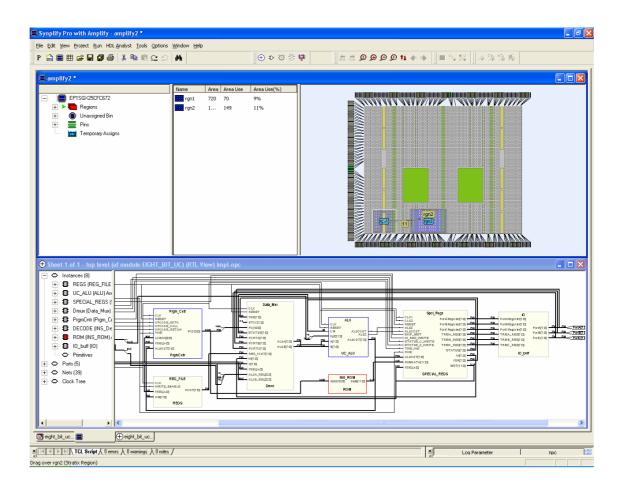

### **Amplify Physical Synthesis**

- Simultaneous placement and optimization

- Integrated Design Planning guides physical optimization

- Boosts performance an average of 20% over synthesis

#### When To Use Amplify

- For fast timing closure

- When you need the highest possible performance

- Need to reduce a speed-grade for cost

- When the majority of delay is in routing

### **Amplify – Interactive Flow**

INNOVATION

### **Types of Physical Constraints**

Module Level Physical Constraints

- Logical module

- Use when critical paths are within logical modules

- Detailed Level Physical Constraints

- Point to point critical path

- Use when critical paths cross module boundaries

OR

- When meeting timing within a module becomes critical

#### **Benefits of Physical Synthesis**

Synthesis with physical constraints provides

- Simultaneous placement and logic optimization

- Placement based optimization

- Register replication for high fanout nets across region boundaries

- Register tunneling across boundaries

- Replication and re-assignment of registers that drive primary I/Os

- Placement of logic constrained to regions

#### Value of Using the Best Synthesis

#### Saves you money

20% premium for 12%-15% performance

Savings are huge for volume applications

#### Makes your products more competitive

- Better performing chips make a better product

- Reaching timing goals quickly gets you to market sooner

#### Design Productivity (Synplify & Synplify Pro)

### **Core Synthesis Technology**

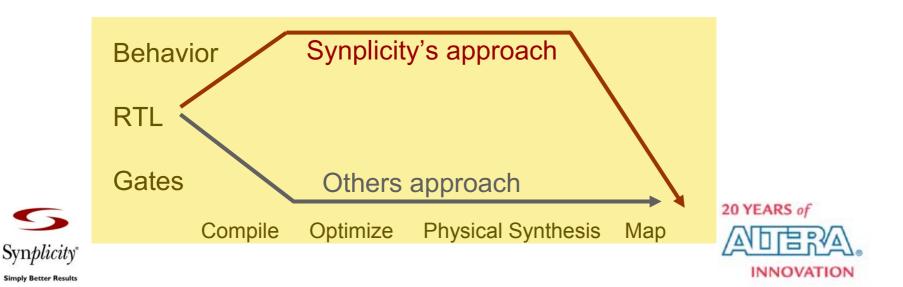

#### ■ BEST<sup>™</sup> – Behavior Extracting Synthesis Technology<sup>®</sup>

- Infers and optimizes behavior from RTL

- Optimizes across hierarchical module boundaries

- Integrated physical synthesis algorithms

- Multi-million gate capacity

- Extremely FAST Unparalleled runtimes

### **Managing Complex Designs**

## MultiPoint<sup>TM</sup>

#### A Powerful Synthesis Flow for

- Incremental design using Synplify Pro or Amplify

- Unlimited gate capacity

- Minimal scripting effort

- No compromise Quality of Results

- Altera Logic Lock flov

### **MultiPoint Flow**

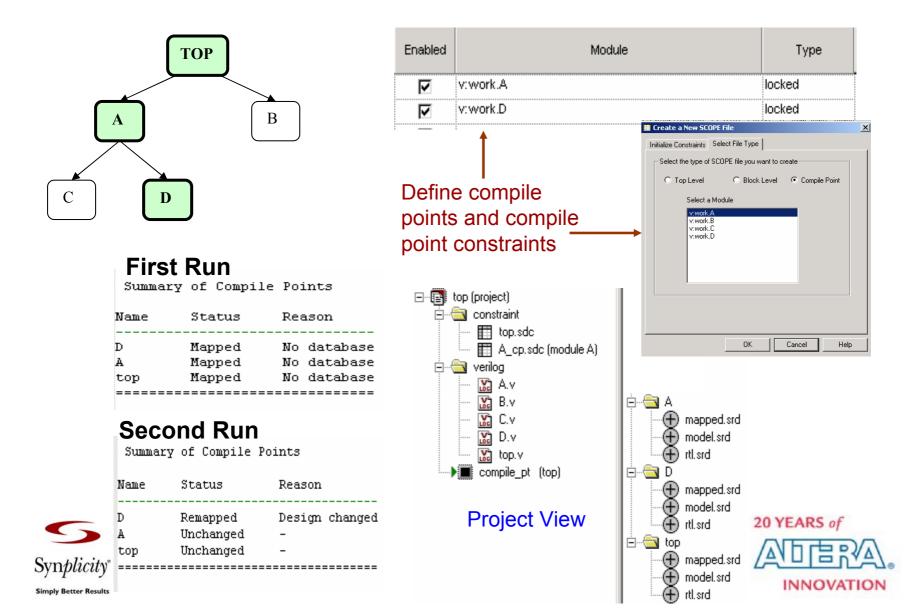

### **MultiPoint Synthesis**

#### **Difference Based Incremental Synthesis**

Re-synthesize a locked Compile Point module for:A logic change in your RTL codeChanges to constraints

- Timing constraints change in the .sdc or Project View

- Project settings change

- FSM Compiler or Explorer

- Retiming

- Pipelining

Re-synthesis is not based on time stamp

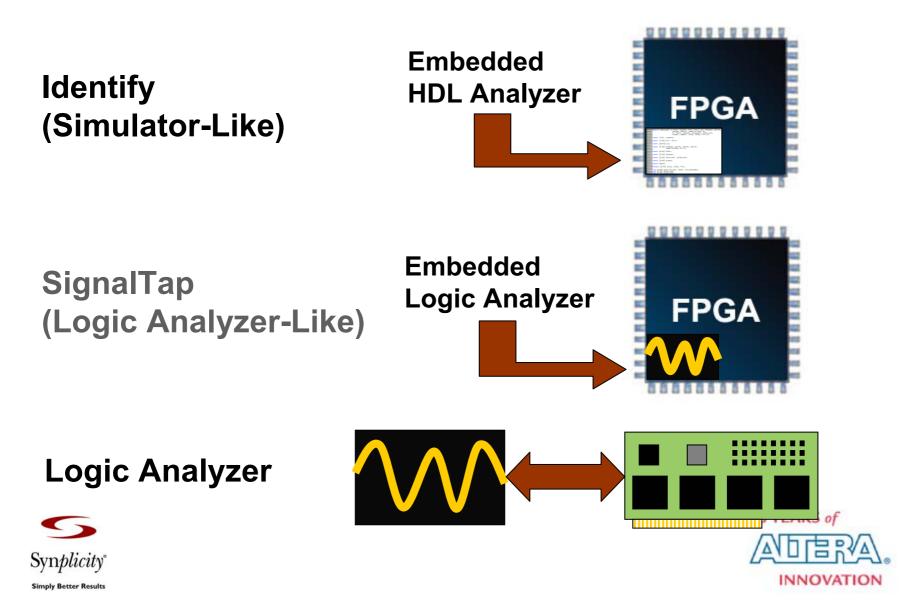

#### Debug (Identify)

#### **Evolution of Hardware Debug**

### **Identify RTL Debugger**

- Debug and instrument FPGA directly in RTL code

- Provides internal visibility in the target system at full speed

- Trigger on Data Path and Control Path

- Standard VCD Output for Waveform Display

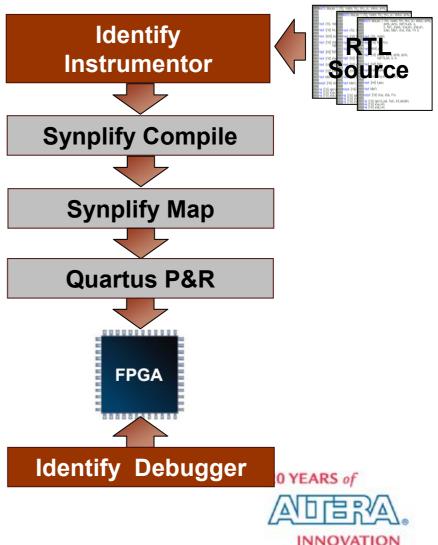

### **Design Flow with Identify**

- Read RTL into Identify Instrumentor

- Compile and map Identify output in Synplify

- FPGA Place & Route

- Use Identify Debugger to view data in FPGA

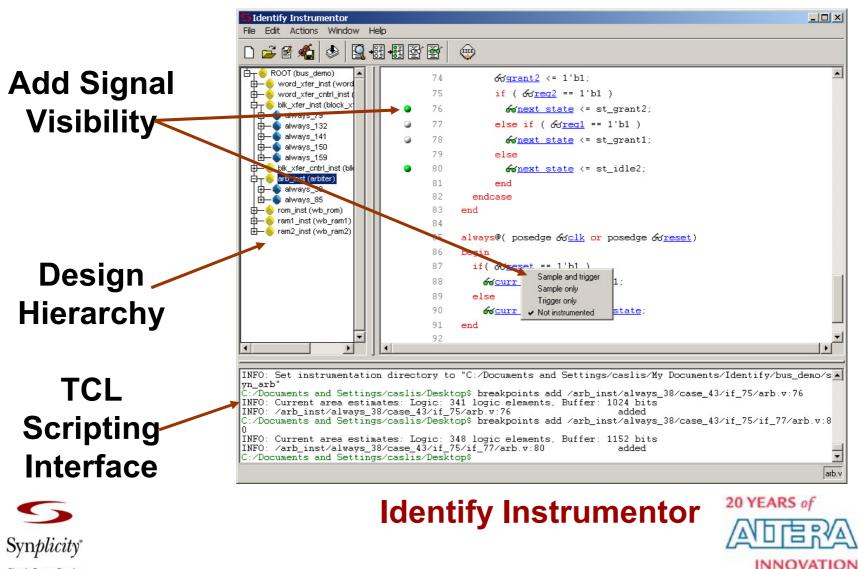

### **Instrumenting for Debug**

**Simply Better Results**

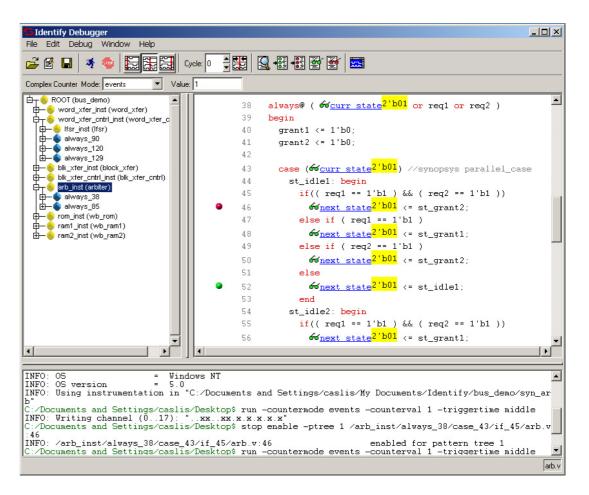

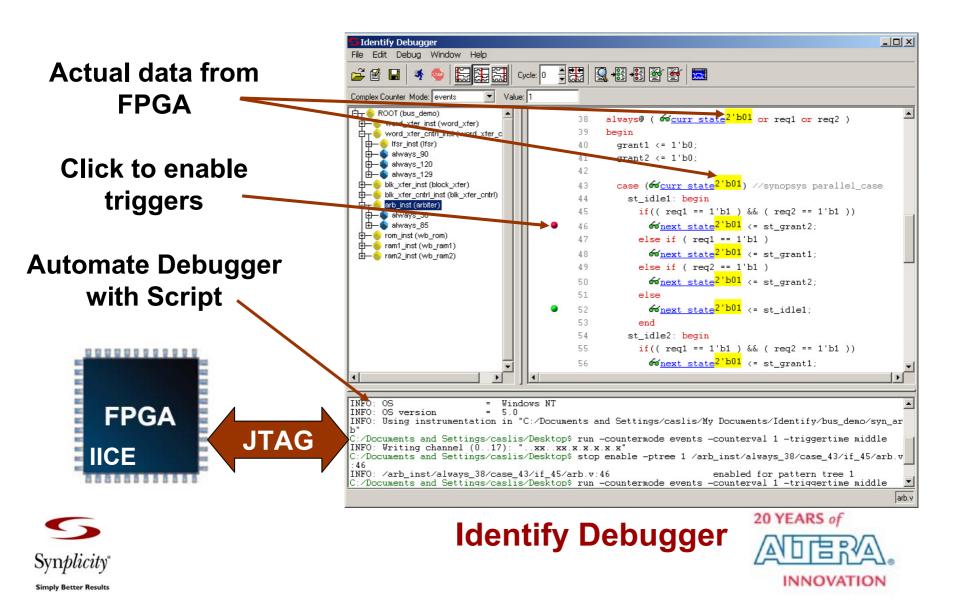

### **Debugging Data From FPGA**

### **RTL Display of Triggers and Sampled Data**

•

- Full support of symbolic values

- Control Path triggers as breakpoints

- Data Path triggers as watch points

- Configurable counters and state machine triggering Control Pa

| 46<br>47 | • grant2'1' <= '0'; Sampled Data<br>From Chip                      |  |

|----------|--------------------------------------------------------------------|--|

| 48       | case ( <b>9</b> <u>curr statest_idle2</u> ) is                     |  |

| 49       | when st_idle1 =>                                                   |  |

| 50       | if ( $\Theta_{reg1}^{'0'} = '1'$ and ( $\Theta_{reg2}^{'1'} = '$   |  |

| 51       | <u>next statestimest_idle2</u> <= st_grant2;                       |  |

| 52       | elsif ( <mark>©<u>req1</u></mark> '0' = '1' ) then                 |  |

| 53       | <u>next statestatestate</u> st_idle2 <= st_grant1;                 |  |

| 54       | elsif ( <sup>●</sup> <u>req2'1' = '1</u> ' ) then                  |  |

| 55       | <u>next state</u> st_idle2 <= st_grant2;                           |  |

| 56       | else                                                               |  |

| 57       | <u>next statestimest_idle2</u> <= st_idle1;                        |  |

| 58       | end if;                                                            |  |

| 59       | when st_idle2 =>                                                   |  |

| 60       | if ( $\Theta_{reg1}^{'0'}$ = '1' ) and ( $\Theta_{reg2}^{'1'}$ = ' |  |

| 61       | <u>next statestimest_idle2</u> <= st_grant1;                       |  |

| 62       | elsif ( <mark>@<u>req1</u></mark> '0' = '1' ) then                 |  |

| 63       | <pre> <u>                                    </u></pre>            |  |

|          |                                                                    |  |

| ath      | Data Path 20 YEARS of                                              |  |

| 😐 Tr     | igger                                                              |  |

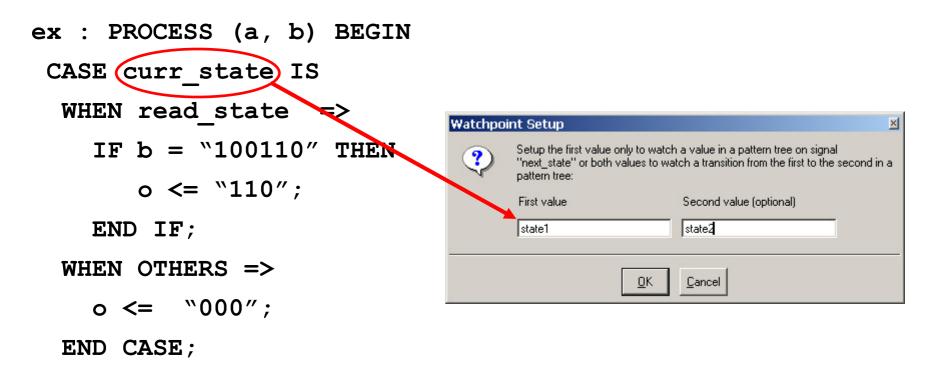

### **Setting Triggers on Data Path**

END PROCESS;

#### **Setting Triggers on Control Path**

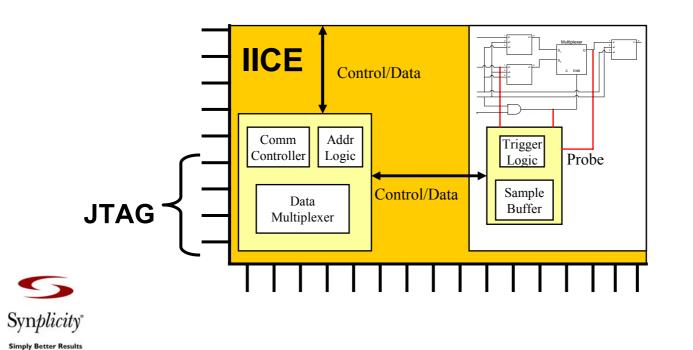

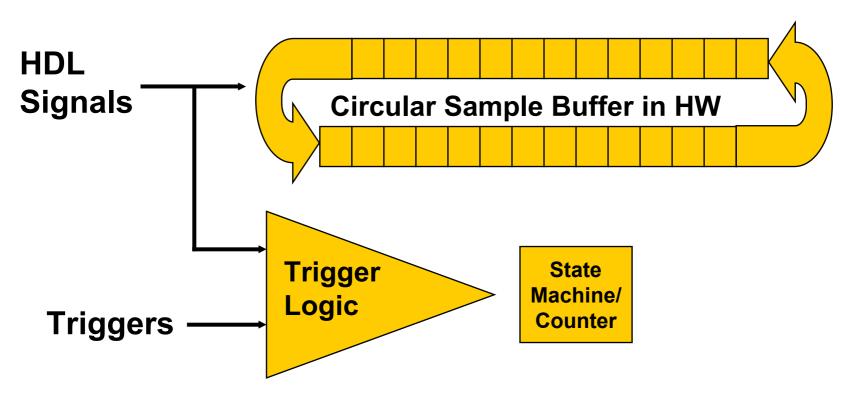

# Intelligent In-Circuit Emulator (IICE)

- Inserted logic used by Instrumentor & Debugger

- Uses dedicated JTAG pins or user-selected pins

- Includes controller, triggering logic, & data storage buffer

### **Triggering Logic and Buffer**

- Trigger values changed dynamically from debugger

- Trigger halts sampling, Not hardware

- Triggers pipelined, only 2 gate delay

#### **Customer Success**

**Foundry Networks**

"In just our first six weeks with the product, we used it to find and fix bugs in three of our designs. In each case the process was completed within a day. It would have taken 10 to 20 times longer using traditional test-bench methods."

-Richard Grenier

**Director of ASIC Development**

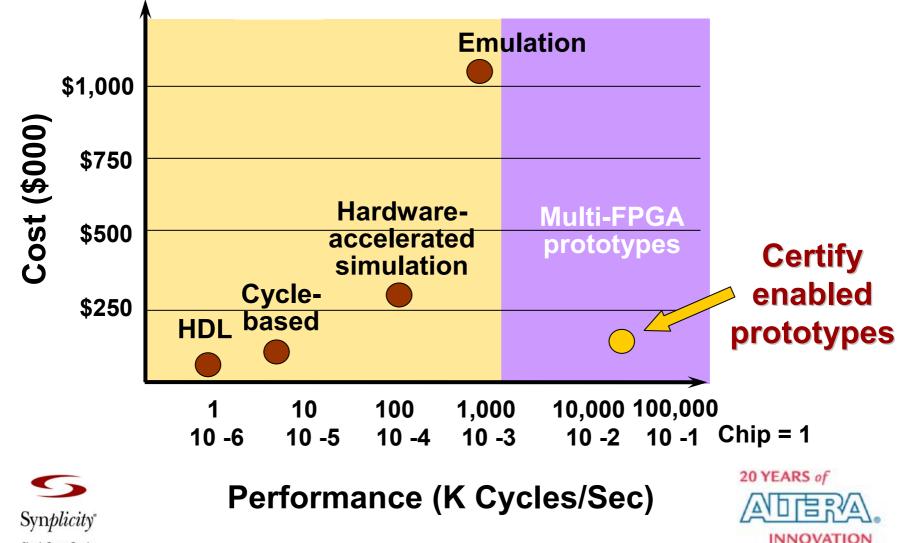

### Multi-FPGA Prototyping (Certify)

### Higher Speed & Lower Cost using FPGA Prototypes

Simply Better Results

#### **Prototyping Challenges**

#### ASIC RTL Code

- Gated Clocks

- DesignWare™

- Performance

- Video and signal processing applications

- Partitioning

- Pin utilization

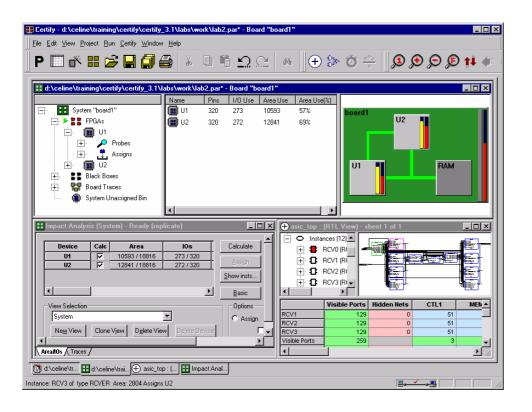

#### **FPGA-Based ASIC Prototypes**

#### Highest performing ASIC prototypes for

- Functional verification

- HW/SW co-verification

- Automatic RTL partitioning, I/O sharing, and more

- Supports all prototyping hardware including off-the-shelf boards

- Adopted by Philips, TI, LSI Logic and others

20 YEARS of

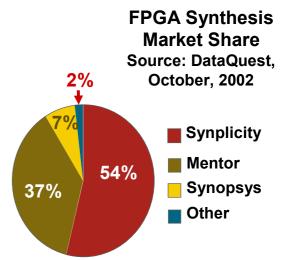

### Summary

- The Market Leader in FPGA synthesis & physical synthesis

- Best Quality of Results

- Unmatched Productivity

- A Leader in EDA innovation

- First in FPGA physical synthesis

- Innovative, at-speed, RT-Level debug technology

- Unique multi-FPGA prototyping system

- Top-ranked customer service and technical support

Synplicity®

**Simply Better Results**