![]()

작성일: 2014.02.26

![]()

게재:2012년07월13일

By David McIntyre

Senior Business Unit Manager

Altera Corporation.

오늘날 엔터프라이즈 스토리지 서브시스템은 근본적인 변화를 겪고 있다. 엔터프라이즈 데이터 및 트랜잭션의 규모가 매년 최대 50~60퍼센트의 속도로 빠르게 증가하고 있다. 이와 같이 급속히 증가하는 데이터 워크로드를 더욱 더 효율적으로 관리하기 위한 수단으로 클라우드 컴퓨팅 및 가상화가 빠르게 확산됨에 따라서 데이터 센터의 수와 규모가 폭발적으로 증가하고 있다. 엔터프라이즈 스토리지가 가파른 속도로 증가하는 것과 더불어서 메모리 서브시스템의 용량과 유용성을 향상시켜야 하는 과제가 제기되고 있다.

시스템 관리자들은 하드 디스크 매체에 주로 의존하는 기존의 스토리지 아키텍처로는 오늘날 워크로드 수요를 충족하기 위한 성능을 제공할 수 없다는 것을 깨닫고 있다. 이러한 문제에 대한 대응으로서 어플리케이션 설계자들은 메모리 아키텍처에 대해서 기존의 스토리지 매체와 엔터프라이즈 분야에 새롭게 등장한 기술로서 플래시 메모리를 결합하는 전체론적 관점의 기법을 도입하고 있다. 오래 전부터 선호되어온 메모리 매체로서 NAND 플래시 메모리는 엔터프라이즈 어플리케이션에 이용했을 때 하드 디스크 드라이브(HDD)에 비해서 10~100배의 성능 향상을 달성할 수 있다. 플래시는 또한 빈번하게 이용하는 데이터 및 어플리케이션에 이용하기 위해서 가장 경제성이 뛰어난 비휘발성 스토리지 매체이기도 하다. 플래시 메모리 어레이를 이용함으로써 기업들은 스토리지 풋프린트를 크게 줄일 수 있고, CPU 및 소프트웨어 라이선스를 줄일 수 있고, 그러므로 결과적으로 데이터 센터의 전력, 공간, 운용 비용을 줄일 수 있다.

이러한 새로운 고성능 메모리 서브시스템의 핵심을 이루는 것이 PLD 기반의 PSM(Programmable State Machine)이다. PSM은 RAID 알고리즘(데이터 무결성을 달성하기 위해서 필수적), 메모리 제어, 고속 I/O 기능을 지원한다. 프로그래머블 로직 디바이스는 근본적인 설계 유연성, 임베디드 프로세서, 하드 구현 메모리 컨트롤러, 고속 직렬 I/O 블록을 특징으로 함으로써 이러한 상태기에 이용하기에 특히 유용하다. PLD 기반 PSM을 이용한 플래시 메모리 아키텍처는 데이터 센터 관리자들이 성능 요구와 데이터 무결성, 시스템 확장성, 서비스 용이성을 적절하게 조화시키면서 스토리지 자원에 대한 갈수록 높아지는 수요를 충족할 수 있도록 한다.

스토리지 계층의 활용

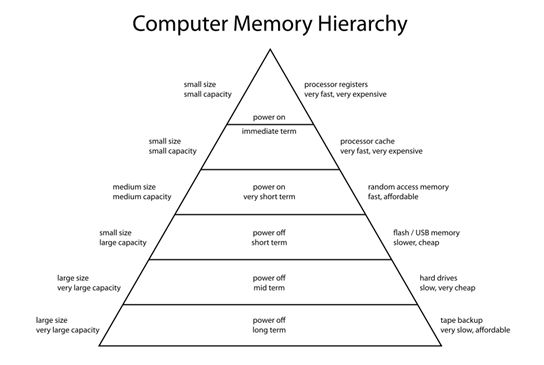

특정한 스토리지 서브시스템에서 각각의 역할을 하는 다양한 메모리 타입을 성능, 비용, 용량을 기준으로 계층적으로 바라볼 수 있다(그림 1). 성능 스펙트럼 상에서 가장 상위 수준에 있는 것은 임베디드 프로세서 메모리와 L1/L2 캐시다. 이 스펙트럼에서 가장 하위 수준에 있는 것은 테잎 백업으로서 이 유형은 매우 낮은 비용으로 매우 높은 용량의 스토리지를 제공하지만 속도가 매우 느리다. 이 둘 사이에 있는 것들이 스토리지 서브시스템에 주로 이용되는 것들이다. 그러한 것들로서 비교적 빠르면서 가격이 비싼 DRAM, 다소 속도는 느리지만 가격이 덜 비싸고 용량이 높은 플래시 RAM, 전통적으로 메모리 시스템에 가장 지배적으로 이용되어온 스토리지 매체로서 HDD가 자리잡고 있다.

|

그림 1: 메모리 계층 |

오늘날의 스토리지 아키텍처는 이 계층에서 혼합적으로 메모리 타입들을 채택하고 있다. 어떤 시스템은 이들 메모리 타입들 전부를 포함할 수도 있고, 또 어떤 시스템들은 일부만을 채택할 수 있다. 특정한 시스템으로 어떠한 메모리 타입들을 어떠한 비중으로 어떻게 혼합할지는 데이터 규모, 프로세싱 워크로드, 기타 요소들에 따라서 결정된다. 엔터프라이즈 데이터 센터 같은 데이터 및 I/O 집중적인 어플리케이션은 다수의 메모리 타입들을 이용할 수 있다. 지금까지도 그랬고 앞으로도 계속해서 대부분의 데이터 스토리지 및 액세스 작업에 HDD 메모리가 이용될 것이다. 하지만 가능한 높은 수준의 성능을 요구하는 “mission critical” 어플리케이션에 있어서는 플래시가 뛰어난 성능과 경쟁력 있는 가격대를 앞세워서 회전 매체(HDD, Tape)를 대체하고 있다.

엔터프라이즈 어플리케이션에 플래시 사용

엔터프라이즈 스토리지 시스템에 플래시를 도입하기 위해서는 해결해야 할 과제들이 있다. 지금까지는 신뢰성 문제가 엔터프라이즈 어플리케이션에 플래시를 이용하는 것을 방해하는 요인이었다. 휴대전화에서 PC에 이르는 여러 전자기기 제품에 플래시가 매우 성공적으로 그리고 보편적으로 사용되면서 이 문제에 대한 염려가 어느 정도 완화되었다. 하지만 소비자 전자기기에서 사용이 입증되었음에도 불구하고 금융 거래 프로세싱 같은 많은 엔터프라이즈 어플리케이션의 특성상 데이터 무결성을 보장할 수 있는 안전조치들을 필요로 한다. 플래시 기반 시스템 디자인에 RAID 알고리즘을 적용함으로써 아주 민감한 어플리케이션이라 하더라도 데이터 무결성을 보장할 수 있을 것이다.

또한 시스템 설계자들이 다중의 플래시 메모리 타입을 다루어야 한다는 것이 또 다른 과제이다. 현재는 주로 multi-level charge 플래시(MLC 플래시)와 single-level charge(SLC 플래시)의 두 가지 유형의 플래시가 이용되고 있다. MLC 플래시는 두 가지 이상의 상태가 가능하고, SLC 플래시는 두 가지 상태만 제공한다. MLC가 또한 SLC보다 가격이 덜 비싸다. 하지만 MLC 플래시는 전압 상태가 변동적이므로 많은 엔터프라이즈 어플리케이션 개발자들은 가격은 좀더 비싸지만 신뢰성이 더 우수한 SLC 플래시를 선택하고 있다. 그렇지만 또 한편으로는 개발자들이 소프트웨어를 통해서 엔터프라이즈 어플리케이션에 더욱 더 경제성 뛰어난 MLC 플래시를 이용할 수 있는 방법들을 찾아내고 있다. RAID 알고리즘과 향상된 ECC 보호 기능을 이용함으로써 MLC의 신뢰성 측면의 위험성을 완화할 수 있게 되었다.

플래시 이외에도 새로운 메모리 타입들이 등장하고 있다. phase change memory(PCM)는 플래시보다 스위칭 시간이 더 빠르고 확장성이 뛰어나다고 주장하는 것으로서 이제 막 태동하기 시작했다. PCM 기술은 현재로서는 플래시의 용량을 제공하지는 못하지만 시간이 지나면 엔터프라이즈 메모리 조합에 이용하기에 현실적으로 가능한 대안을 제공할 수 있을 것이다. 이러한 다중의 메모리 타입을 관리하고 새롭게 등장하는 기술들을 활용하기 위해서는 메모리 어레이 서브시스템 설계 시에 메모리 제어와 관리를 위해서 프로그래머블 로직 디바이스의 유연성과 적응성이 매우 유용하게 이용될 수 있을 것이다.

플래시 메모리 액세스 속도가 또 다른 고려사항이다. 흔히 I/O와 액세스 속도가 메모리 시스템 성능을 제한하는 요소가 될 수 있다. 서버 팜과 시스템 사이에 효율적인 접속을 제공하는 PCI Express(PCIe) 같은 표준을 지원하는 것이 중요하다. 그런데 이와 같은 표준들이 이들이 상호작용하는 메모리 타입과 발맞추어서 빠르게 진화하고 있다. 그러므로 어떠한 플래시 기반 서브시스템이든 이와 같은 변동성을 고려해야만 한다. PLD는 특히 PCIe 코어와 그 밖의 최적화 인터페이스들을 제공함으로써 변화하는 표준을 따라잡고 대처할 수 있는 민첩성을 제공한다.

FPGA 기술

플래시 메모리 어레이의 메모리 제어 기능 및 I/O 인터페이스를 구현하기 위한 기술을 고려할 때는 여러 가지 기술들을 신중하게 검토해야 한다. ASSP나 ASIC 디바이스 같은 기존의 기술은 빠르게 변화하는 플래시 시장에 요구되는 유연성을 제공하지 못한다. ASIC은 또한 대부분의 어플리케이션에 이용하기에 엄청나게 비싸다. 플래시 메모리를 활용하고자 하는 스토리지 서브시스템 개발자들은 진화하는 메모리 타입 및 변화하는 표준에 신속하게 대응하고 적응할 수 있는 민첩성을 필요로 한다.

FPGA 같은 프로그래머블 IC는 플래시 기반 엔터프라이즈 어플리케이션에 이용하기에 이상적으로 적합하다. 근본적으로 빠르고, 비용이 낮고, 위험성이 낮은 FPGA 개발 작업은 변화하는 요구에 빠르게 대응할 수 있을 뿐만 아니라 메모리 기술이나 PCIe 같은 인터페이스 표준에 있어서 변화하는 기술들을 빠르게 활용할 수 있다. 또한 오늘날 프로그래머블 디바이스는 높은 용량을 제공함에 따라서 예를 들어서 서브시스템이 MLC 플래시와 SLC 플래시를 동시에 지원하는 경우와 같이 다중의 메모리 타입을 지원하기 위한 제어 및 인터페이스를 설계할 수 있게 되었다. 또한 결함 허용 RAID 알고리즘을 FPGA 로직으로 편리하게 구현할 수 있다.

FPGA는 이전에는 ASIC으로만 독점적으로 가능한 것으로 여겨졌었던 성능 및 맞춤화 상의 이점을 제공한다. 오늘날 PLD는 가장 최신의 실리콘 프로세스 노드로 제조되므로 최신의 반도체 기술을 이용해서 가장 우수한 성능을 제공한다. 예를 들어서 이제 28nm PLD 인터페이스는 전송 속도가 최대 28Gbps에 이르는 고속 데이터 트래픽 허브를 통해서 데이터를 전송할 수 있게 됨으로써 PCIe, SAS/SATA, Fibre Channel 같은 매우 높은 속도의 프로토콜의 성능 요구까지도 충족할 수 있게 되었다. FPGA는 또한 메모리 컨트롤러, 임베디드 프로세서, 트랜시버 블록 등의 소프트 및 하드 IP 코어를 제공하므로 성능을 더욱 더 향상시키고, 풍부한 기능을 구현하고, 효율을 향상시킬 수 있다. 또한 PLD 패키징 기술의 발전으로 많은 수의 범용 I/O 핀뿐만 아니라 고속 I/O 포트를 제공할 수 있게 되었다.

프로그래머블 상태기를 이용한 플래시 캐시

메모리 어레이 업체인 Violin Memory는 차세대 24x7 가동 엔터프라이즈 데이터 센터의 요구를 충족하면서 낮은 비용으로 확장이 가능하도록 다음과 같은 특성의 메모리 어레이를 설계하고자 한다.

이러한 특성들은 GB당 비용이 낮은 NAND 플래시 메모리를 기반으로 한 새로운 유형의 스토리지 어레이를 이용해서 구현할 수 있다. 이 아키텍처는 2개 레벨의 플래시 기능, 플래시 제어(vFLASH), 플래시 RAID(vRAID)를 채택한다. 플래시 컨트롤러는 플래시 기술 읽기, 쓰기, 소거 동작과 플래시 변환 층에서 비트, 블록, 플레인, 칩 레벨의 오류 조건을 이용한다. vFLASH 기능은 로그 구조 데이터 레이아웃과 공간을 비워놓기 위한 플래시 관리 “garbage collection” 기능을 포함한다. 플래시 메모리에 이용하는 RAID 컨트롤러는 플래시의 고유의 특성들을 충족하기 위해서 전통적인 RAID-1 및 RAID-5 알고리즘 이상을 거쳐야 한다. 예를 들어서 4+1 패리티 모델은 전통적인 알고리즘보다 훨씬 더 효율적이고 지연시간이 낮으며, 또한 모듈 교체를 필요로 하지 않고 결함에 더욱 더 효과적으로 대처할 수 있다.

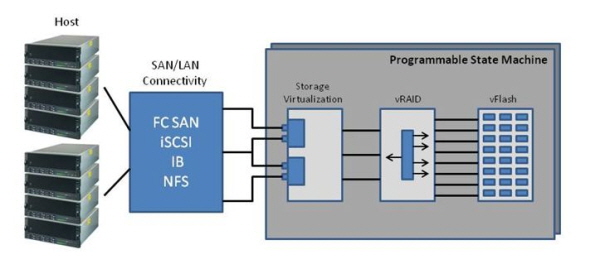

플래시와 RAID 제어를 FPGA 기술로 효과적으로 구현할 수 있다(그림 2). 주요 알고리즘을 전통적인 마이크로프로세서/소프트웨어 기법이 아니라 실리콘 기반 상태기로 구현함으로써 훨씬 더 낮은 지연시간을 달성할 수 있다. 또한 앞서 언급했듯이 FPGA 기반 구현은 설계 유연성이 뛰어나므로 빠르게 변화하는 플래시 및 관련 기능들에 따라서 빠르게 적응할 수 있다. 그러므로 새로운 디자인을 매우 신속하게 매우 낮은 비용으로 시장에 선보일 수 있으며 그럼으로써 새로운 기회들을 남보다 앞서 포착할 수 있다. 또한 메모리 컨트롤러, 트랜시버 블록, 메모리와 PCIe 카드에 대한 고속 인터페이스 같은 FPGA 기능들을 활용함으로써 기존의 기법을 이용할 때와 비교해서 훨씬 더 빠르게 수일 또는 수일 이내에 고도로 최적화된 시스템을 시장에 내놓을 수 있다.

|

그림 2: 메모리 서브시스템 블록 다이어그램 |

엔터프라이즈 스토리지의 새로운 패러다임

오늘날 엔터프라이즈 스토리지 시스템은 경쟁력 향상을 위해서 플래시 메모리 기술의 성능 및 비용 상의 이점을 필요로 한다. 메모리 관리 및 I/O에 FPGA 기반 PSM을 이용함으로써 플래시를 이용할 때 데이터 무결성을 달성하거나 새롭게 등장하는 메모리 타입 및 변화하는 표준을 충족하는 것과 같은 고유의 설계 과제들을 편리하게 해결할 수 있을 것이다. FPGA 기술과 플래시 메모리 기술을 결합함으로써 스토리지 시스템 설계자들은 오늘날 아주 까다로운 워크로드에 이르기까지 요구되는 성능 수준을 달성하고 시스템 무결성, 확장성, 민첩한 적응성을 달성할 수 있을 것이다.

![]()