# Two-Way Mixed-Voltage Interfacing of Actel's SX FPGAs

# Introduction

In the past, bipolar circuits with a 5V standard power supply voltage dominated digital system designs. CMOS IC manufacturers adopted this power supply voltage, and most system components are still available in the 5V version. In order to achieve even higher speeds and densities at a lower cost and with lower power consumption, the CMOS IC manufacturers have developed advanced deep-submicron fabrication, thinner gate oxides, and process geometries as small as  $0.25 \mu m$ , with  $0.18 \mu m$  expected in the future.

The disadvantage of designing submicron devices using a 5V power supply voltage is the high-field-effect failure resulting from hot-carrier injection. To decrease these failures, a lower supply voltage was needed to power up these new devices, leading to the introduction of the 3.3V standard power supply voltage devices. This necessitated two-way mixed-voltage interfacing to support the existing 5V standard power supply system designs.

This Application Note describes the two-way mixed-voltage interfacing specifications available in Actel's SX family of FPGAs. SX devices support I/Os that can be used as either regular I/Os or as PCI compliant I/Os. With specific I/O designs, the 54SX16P can meet the two-way mixed-voltage interfacing design requirement. Furthermore, the 54SX16P can be configured to meet the PCI compliant specification. Table 2, Table 3, and Table 4 on page 2 list the DC electrical characteristics of the SX FPGAs.

# **TTL Interface Levels**

Table 1

SX Operating Configuration

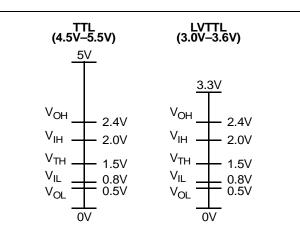

Figure 1 shows the standard TTL (5V) and LVTTL (3.3V) DC interface levels. Both standards use the same interface voltage levels.

*Figure 1* • 5V(TTL) and 3.3V(low-voltage TTL) Interfaces

# 54SX08, 54SX16, and 54SX32 Operating Mode

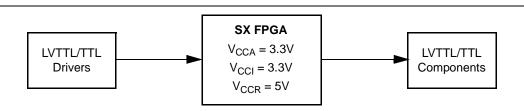

To ensure that the 54SX08, 54SX16, and 54SX32 devices can be utilized in different systems, they have been designed to meet various system interface requirements. Table 1 shows the required  $V_{CCA}$ ,  $V_{CCI}$ , and  $V_{CCR}$  operating voltages.

The 54SX08, 54SX16, and 54SX32 devices accept LVTTL/TTL signals on all inputs, and the outputs can drive any LVTTL/TTL devices. The  $V_{\rm CCA}$  and  $V_{\rm CCI}$  pins must be suplied with 3.3V, while the  $V_{\rm CCR}$  pin must be supplied with 5V. The outputs are only driven up to 3.3V. Figure 2 shows the operating configuration that is intended for mixed LVTTL/TTL systems.

| Description | V <sub>CCA</sub> | V <sub>CCI</sub> | V <sub>CCR</sub> | Input Voltage Tolerance | Output Voltage (Max) |

|-------------|------------------|------------------|------------------|-------------------------|----------------------|

| LVTTL/TTL   | 3.3V             | 3.3V             | 5V               | 3.3V/5V                 | 3.3V                 |

Figure 2 • SX Operating Mode for Mixed LVTTL/TTL Systems

|                  |                                              | Commercial               |                  | Industrial               |                  |       |

|------------------|----------------------------------------------|--------------------------|------------------|--------------------------|------------------|-------|

| Symbol           | Parameter                                    | Min.                     | Max.             | Min.                     | Max.             | Units |

| V <sub>CCA</sub> | Supply Voltage for Array                     | 3.0                      | 3.6              | 3.0                      | 3.6              | Volts |

| V <sub>CCI</sub> | I/O Supply Voltage                           | 3.0                      | 3.6              | 3.0                      | 3.6              | Volts |

| V <sub>CCR</sub> | Supply Voltage required for Internal Biasing | 4.75                     | 5.25             | 4.5                      | 5.5              | Volts |

| V <sub>IL</sub>  | Input Low Voltage                            |                          | 0.8              |                          | 0.8              | Volts |

| VIH              | Input High Voltage                           | 2.0                      |                  | 2.0                      |                  | Volts |

|                  | $I_{OL} = 20 \ \mu A \ (CMOS)$               |                          | 0.1              |                          |                  | Volts |

| V <sub>OL</sub>  | $I_{OL} = 12 \text{ mA}(TTL)$                |                          | 0.5              |                          |                  | Volts |

|                  | $I_{OL} = 8$ mA (TTL)                        |                          |                  |                          | 0.5              | Volts |

|                  | $I_{OH} = -20 \ \mu A \ (CMOS)$              | (V <sub>CCI</sub> – 0.1) | V <sub>CCI</sub> | (V <sub>CCI</sub> – 0.1) | V <sub>CCI</sub> | Volts |

| V <sub>OH</sub>  | $I_{OH} = -8 \text{ mA} (TTL)$               | 2.4                      | V <sub>CCI</sub> |                          | 001              | Volts |

| -                | $I_{OH} = -6$ mA (TTL)                       |                          |                  | 2.4                      | V <sub>CCI</sub> | Volts |

Table 2 • DC Electrical Characteristics for 54SX08, 54SX16, 54SX32, and 54SX16P

Table 3 • 5V PCI DC Electrical Characteristics for 54SX16P

|                  |                                                             | Com  |                        |       |

|------------------|-------------------------------------------------------------|------|------------------------|-------|

| Symbol           | Parameter and Condition                                     | Min. | Max.                   | Units |

| V <sub>CCA</sub> | Supply Voltage for Array                                    | 3.0  | 3.6                    | Volts |

| V <sub>CCI</sub> | I/O Supply Voltage                                          | 4.75 | 5.25                   | Volts |

| V <sub>CCR</sub> | Supply Voltage required for Internal Biasing                | 4.75 | 5.25                   | Volts |

| V <sub>IL</sub>  | Input Low Voltage                                           | -0.5 | 0.8                    | Volts |

| V <sub>IH</sub>  | Input High Voltage                                          | 2.0  | V <sub>CCI</sub> + 0.5 | Volts |

| IIL              | Input Low Leakage Current V <sub>IN</sub> = 0.5V            |      | -70                    | μA    |

| I <sub>IH</sub>  | Input High Leakage Current V <sub>IN</sub> = 2.7V           |      | 70                     | μA    |

|                  | Output Low Voltage                                          |      |                        |       |

| V <sub>OL</sub>  | I <sub>OL</sub> = 3 mA (signals without pull up resistor)   |      | 0.55                   | Volts |

|                  | I <sub>OL</sub> = 6 mA (signals requiring pull up resistor) |      | 0.55                   | Volts |

| V <sub>OH</sub>  | Output High Voltage $I_{OH} = -2 \text{ mA}$                | 2.4  |                        | Volts |

Table 4•3.3V PCI DC Electrical Characteristics for 54SX16P

| Com                 |                        |       |  |

|---------------------|------------------------|-------|--|

| Min.                | Max.                   | Units |  |

| 3.0                 | 3.6                    | Volts |  |

| 3.0                 | 3.6                    | Volts |  |

| 3.0                 | 3.6                    | Volts |  |

| -0.5                | 0.3V <sub>CCI</sub>    | Volts |  |

| 0.5V <sub>CCI</sub> | V <sub>CCI</sub> + 0.5 | Volts |  |

|                     | 0.7V <sub>CC</sub>     |       |  |

|                     | ±10                    | μA    |  |

|                     | 0.1V <sub>CCI</sub>    | Volts |  |

| 0.9V <sub>CCI</sub> |                        | Volts |  |

|                     | 0.9V <sub>CCI</sub>    |       |  |

Note: 1.

This specification should be guaranteed by design. It is the minimum voltage to which pull-up resistors are calculated to pull a floated network. Applications sensitive to static power utilization should assure that the input buffer is conducting minimum current at this input voltage.

# 54SX16P Operating Modes

The 54SX16P FPGA has added system flexibility because it has been designed with three operating modes as shown in Table 5.

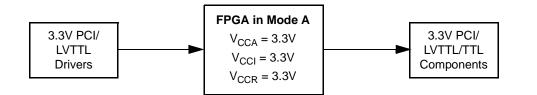

# Mode A (3.3V PCI/LVTTL)

In Mode A, the 54SX16P device accepts 3.3V PCI/LVTTL signals on all inputs, and the outputs can drive any 3.3V PCI/ LVTTL/TTL devices. The  $V_{CCA}$ ,  $V_{CCI}$ , and  $V_{CCR}$  pins must be supplied with 3.3V. This mode is intended for 3.3V PCI/LVTTL systems. Figure 3 shows the Mode A configuration.

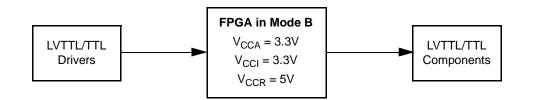

#### Mode B (Mixed LVTTL/TTL)

In Mode B, the 54SX16P device accepts LVTTL/TTL signals on all inputs, and the outputs can drive any LVTTL/TTL devices. The  $V_{\rm CCA}$  and  $V_{\rm CCI}$  pins must be supplied with 3.3V, while the  $V_{\rm CCR}$  pin must be supplied with 5V. This mode is intended for mixed LVTTL/TTL systems. Figure 4 shows the Mode B configuration.

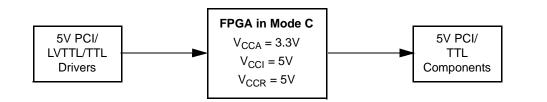

# Mode C (5V PCI/ TTL)

In Mode C, the 54SX16P device accepts 5V PCI/LVTTL/TTL signals on all inputs, and the outputs can drive any 5V PCI/TTL devices. The  $V_{\rm CCA}$  pins must be supplied with 3.3V, while the  $V_{\rm CCI}$  and  $V_{\rm CCR}$  must be supplied with 5V. This mode is intended for 5V PCI and TTL systems. The output can be driven up to 5V. Figure 5 shows the Mode C configuration.

| Modes | Description    | V <sub>CCA</sub> | V <sub>CCI</sub> | V <sub>CCR</sub> | Input Voltage Tolerance | Output Voltage (Max) |

|-------|----------------|------------------|------------------|------------------|-------------------------|----------------------|

| A     | 3.3V PCI/LVTTL | 3.3V             | 3.3V             | 3.3V             | 3.3V                    | 3.3V                 |

| В     | MixedLVTTL/TTL | 3.3V             | 3.3V             | 5V               | 5V                      | 3.3V                 |

| С     | 5V PCI/TTL     | 3.3V             | 5V               | 5V               | 5V                      | 5V                   |

Table 5 • 54SX16P Operating Mode

Figure 3 • Mode A Configuration

Figure 4 • Mode B Configuration

Figure 5 • Mode C Configuration

#### **Two-way Mixed-Voltage Interfacing**

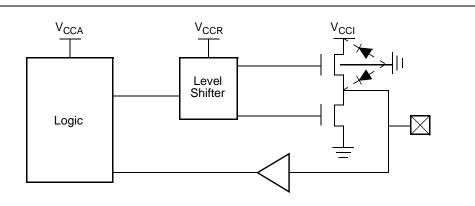

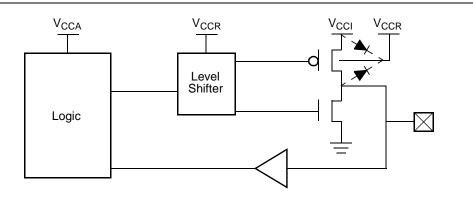

The 54SX08, 54SX16, and 54SX32 are designed with an N-channel pull-up through the I/Os. The circuit design is shown in Figure 6. Additionally, the 54SX16P flexible I/Os are designed with a P-channel pull up, as shown in Figure 7. These I/Os can be driven to either 3.3V or 5V to support two-way mixed-voltage interfacing.

The order in which the power supplies are ramped up and ramped down is critical for all SX devices. To avoid device damage,  $V_{CCR}$  must be greater than or equal to  $V_{CCI}$  at all times. This guideline applies to both power-up and power-down sequences. A p-n junction exists between the  $V_{CCI}$  and  $V_{CCR}$  power supplies in the circuitry of the JTAG TDI and TMS pins. When  $V_{CCI}$  is greater than  $V_{CCR}$  by 0.6V,

the p-n junction will forward bias and cause excessive current flow. The excessive current through the p-n junction may damage the TDI and TMS pin circuitry. For more information about power-up and power-down of SX devices, refer to the "Power-up and Power-Down Behavior of SX and RT54SX Devices" Application Note.

#### Conclusion

Most systems currently use 5V and 3.3V devices. To support this design trend, new devices must support two-way mixed-voltage interfacing. Actel offers a solution with its SX family of FPGAs.

Figure 6 • SX I/Os with N-channel Pull-up

Figure 7 • SX I/Os with P-channel Pull-up

Actel and the Actel logo are registered trademarks of Actel Corporation. All other trademarks are the property of their owners.

http://www.actel.com

# Actel Europe Ltd.

Maxfli Court, Riverside Way Camberley, Surrey GU15 3YL United Kingdom Tel: +44 (0)1276 401450 Fax: +44 (0)1276 401590

# Actel Corporation

955 East Arques Avenue Sunnyvale, California 94086 USA **Tel:** (408) 739-1010 **Fax:** (408) 739-1540 Actel Asia-Pacific EXOS Ebisu Bldg. 4F 1-24-14 Ebisu Shibuya-ku Tokyo 150 Japan Tel: +81-(0)3-3445-7671 Fax: +81-(0)3-3445-7668